Rev. 2.0 — 23 June 2021

application note

#### **Document information**

| Information | Content                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | Low VCEsat, BISS, thermal resistance (Rth), thermal impedance (Zth), total power dissipation (Ptot)                                                                                                                            |

| Abstract    | This application note illustrates how to improve the power dissipation of discrete components by using multilayer PCBs. It focuses on the impact of using larger copper areas to improve the thermal behavior of applications. |

#### Thermal behavior of small-signal discretes on multilayer PCBs

#### 1. Introduction

In today's data sheets thermal characteristics are measured on a standard FR4 single copper layer Printed-Circuit Board (PCB). Customers should be able to compare devices easily just by evaluating standard data sheet parameters. In reality, design engineers cannot only rely on data sheet parameters and must consider the individual design requirements.

#### 2. Thermal resistance

### 2.1. Key parameters

The main thermal parameters for semiconductor device are junction temperature  $(T_j)$  and thermal resistance  $(R_{th})$ . Thermal resistance depends on the environment surrounding a semiconductor device. In data sheets, design engineers can find different thermal resistances (see Section 2.1.1 and Section 2.1.2).

Thermal resistance of semiconductor devices is defined in general as:

$$R_{th(x)} = \frac{T_j - T_x}{P_{tot}} \tag{1}$$

Where:

$R_{th(x)}$  = thermal resistance from the device junction to specific environment [K/W]

T<sub>i</sub> = device junction temperature in steady state [°C]

T<sub>x</sub> = reference temperature of the specific environment [°C]

P<sub>tot</sub> = maximum power dissipation of the semiconductor device [W].

Thermal data is not comparable, unless a semiconductor supplier provides all test conditions. Nexperia Semiconductors provides them. They are often marked with a note at the end of an abstract or table, in the data sheet.

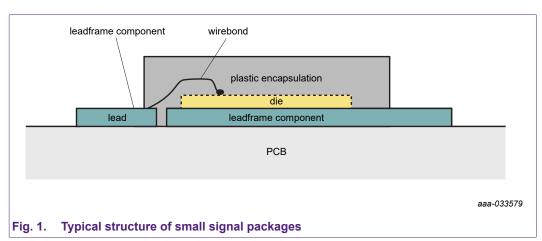

Fig. 1 shows the typical structure of small signal devices. The heat is generated at the junction and must be transferred by the leadframe to the outside of the package. Thermal conduction between the die and the leadframe and between the leadframe and the PCB allow this transfer. The heat transfer between PCB and air can be done by convection and/or radiation.

#### 2.1.1. Thermal resistance from junction to solder point

This parameter depends on the component. The size of the die, the material of the leadframe and the mold compound influence the  $R_{th(j-sp)}$ . The solder point is defined as the mounting point where the device would be normally soldered to the PCB. It is a conduction path only.

AN11076

#### Thermal behavior of small-signal discretes on multilayer PCBs

### 2.1.2. Thermal resistance from junction to ambient R<sub>th(i-a)</sub>

This parameter describes the thermal resistance from the junction (die) to the ambient. It is a single thermal resistance value including all effects of possible series and parallel paths from the junction to the ambient. Typically, it includes all the heat transfer methods of conduction and convection, from the surface of the package and via the PCB.

R<sub>th(j-a)</sub> is only valid for a specific PCB and not for:

- · PCBs of different size, shape or layer stack to the test specification

- · Several devices mounted on one PCB

- Operation within a housing, which influences the convection

- · Forced cooling, for example, by cooling fan

#### 3. Heat transfer mechanism

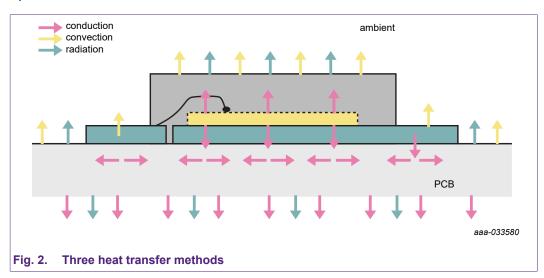

Up to three different transfer methods can be used to transfer heat from the die to the ambient.

#### 3.1. Thermal conduction

Conduction is a heat transfer in a medium due to a temperature change. For small-signal discrete components the heat transfer between the die and the leadframe and then the leadframe and the PCB is done by conduction.

#### 3.2. Thermal convection

Convection is a heat transfer from a body due to the movement of a medium, which is in contact with the surface of the body. In our case, it is the transfer of heat from the PCB surface and the ambient air. Due to the poor thermal conductivity of the plastic package, the main path for convection is the PCB/air interface.

#### 3.3. Thermal radiation

Radiation is a heat transfer by emitting heat from a hot body, which will be absorbed by a cooler one. For example PCB surface and surrounding objects such as the side panel of the housing.

AN11076

#### Thermal behavior of small-signal discretes on multilayer PCBs

### 4. Thermal measurement results

In PCB design, the numbers of variables are significant. The thermal resistance depends on board size, thickness, cooling pad area and ambient temperature.

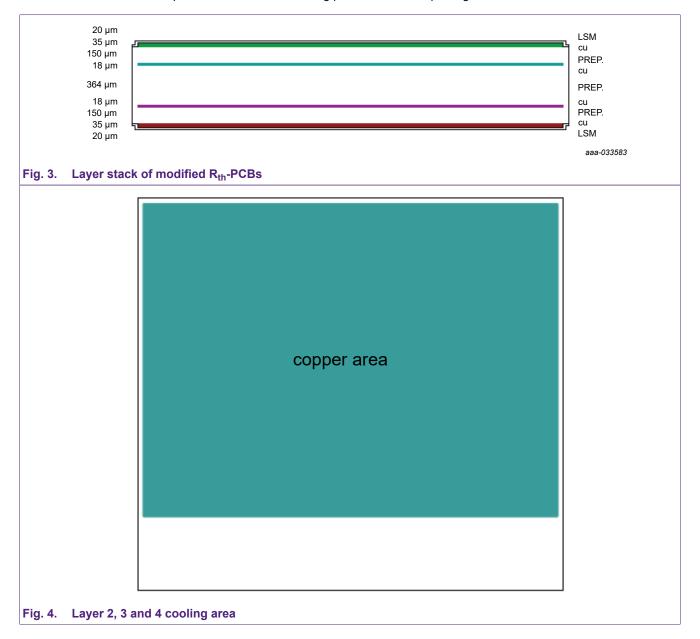

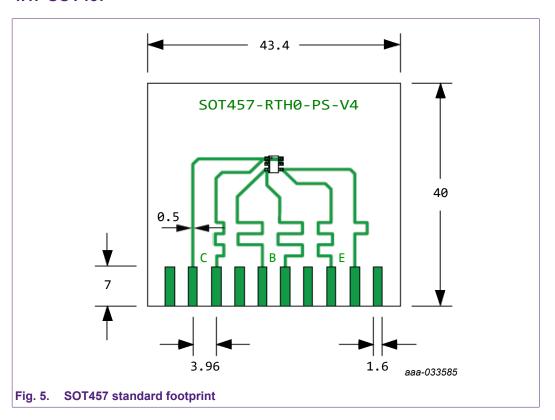

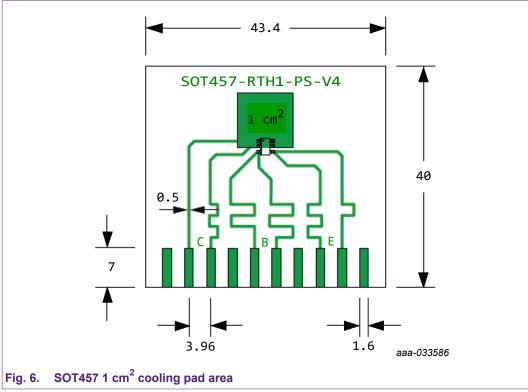

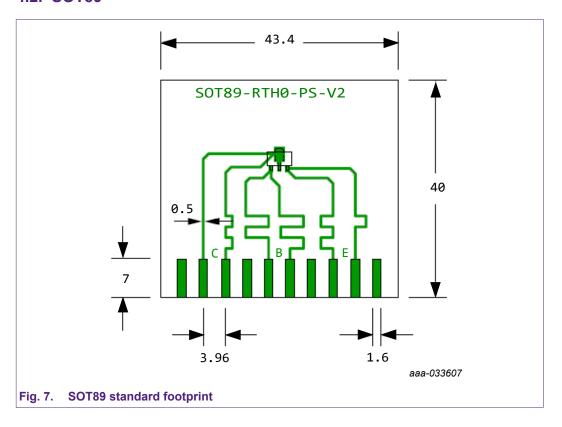

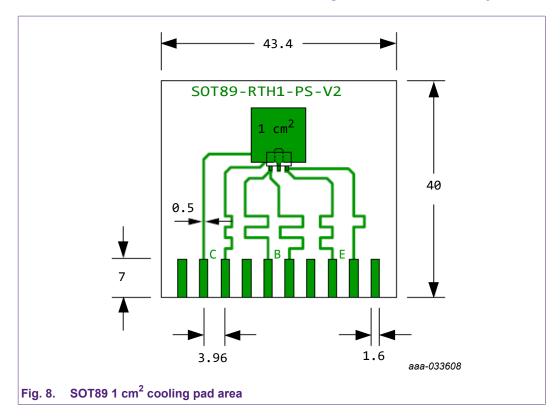

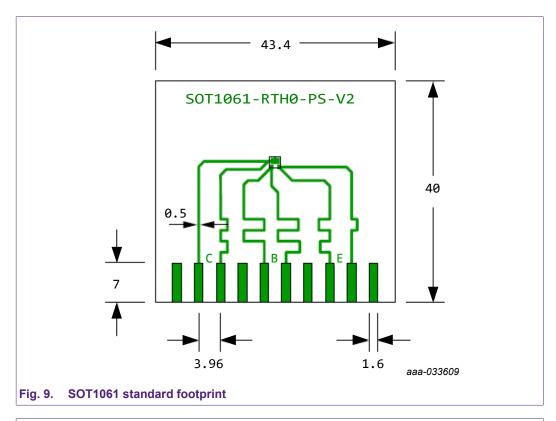

Therefore, Nexperia Semiconductors has developed specific  $R_{th}$ -PCBs which are according to the JEDEC standards. It helps designers to compare easily relevant thermal parameters from different small-signal discrete vendors. Unfortunately, most applications are not developed on single layer FR4 PCBs. To get a better view of customer requirements, Nexperia Semiconductors set up a four-layer PCB. All PCBs differ by the top layer layout. Layers 2 to 4 consist of pure copper layers with a dimension of approximately  $32 \times 42$  mm (see Fig. 4). The top layer design was made on standard footprint and with a 1 cm<sup>2</sup> cooling pad area for each package.

### Thermal behavior of small-signal discretes on multilayer PCBs

### 4.1. SOT457

5/14

### Thermal behavior of small-signal discretes on multilayer PCBs

Table 1. PBSS5350D in SOT457; typical values

| Sample              | Standard footprint    |                       | 1 cm <sup>2</sup> coolin | 1 cm <sup>2</sup> cooling pad |  |

|---------------------|-----------------------|-----------------------|--------------------------|-------------------------------|--|

|                     | R <sub>th</sub> (K/W) | P <sub>tot</sub> (mW) | R <sub>th</sub> (K/W)    | P <sub>tot</sub> (mW)         |  |

| 1                   | 181                   | 689                   | 141                      | 889                           |  |

| 2                   | 181                   | 689                   | 141                      | 889                           |  |

| 3                   | 181                   | 689                   | 141                      | 889                           |  |

| Average             | 181                   | 689                   | 141                      | 889                           |  |

| +15 % safety margin | 208                   | 600                   | 162                      | 770                           |  |

| Single layer FR4    | 275                   | 450                   | 208                      | 600                           |  |

## 4.2. SOT89

### Thermal behavior of small-signal discretes on multilayer PCBs

Table 2. PBSS5330X in SOT89; typical values

| Sample              | Standard for          | Standard footprint    |                       | 1 cm <sup>2</sup> cooling pad |  |

|---------------------|-----------------------|-----------------------|-----------------------|-------------------------------|--|

|                     | R <sub>th</sub> (K/W) | P <sub>tot</sub> (mW) | R <sub>th</sub> (K/W) | P <sub>tot</sub> (mW)         |  |

| 1                   | 79                    | 1582                  | 47                    | 2660                          |  |

| 2                   | 77                    | 1623                  | 42                    | 2976                          |  |

| 3                   | 72                    | 1736                  | 43                    | 2907                          |  |

| Average             | 76                    | 1647                  | 44                    | 2848                          |  |

| +15 % safety margin | 88                    | 1420                  | 51                    | 2450                          |  |

| Single layer FR4    | 225                   | 550                   | 125                   | 1000                          |  |

### Thermal behavior of small-signal discretes on multilayer PCBs

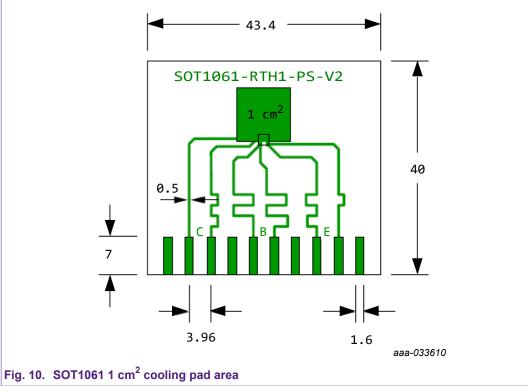

### 4.3. SOT1061

### Thermal behavior of small-signal discretes on multilayer PCBs

Table 3. PBSS5330PA in SOT1061; typical values

| Sample              | Standard footprint    |                       | 1 cm <sup>2</sup> coolin | 1 cm <sup>2</sup> cooling pad |  |

|---------------------|-----------------------|-----------------------|--------------------------|-------------------------------|--|

|                     | R <sub>th</sub> (K/W) | P <sub>tot</sub> (mW) | R <sub>th</sub> (K/W)    | P <sub>tot</sub> (mW)         |  |

| 1                   | 114                   | 1096                  | 50                       | 2500                          |  |

| 2                   | 113                   | 1106                  | 51                       | 2541                          |  |

| 3                   | 111                   | 1126                  | 52                       | 2404                          |  |

| Average             | 112                   | 1116                  | 51                       | 2541                          |  |

| +15 % safety margin | 129                   | 970                   | 59                       | 2110                          |  |

| Single layer FR4    | 250                   | 500                   | 125                      | 1000                          |  |

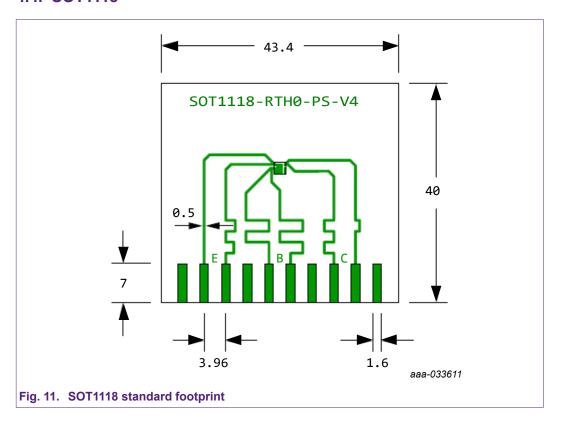

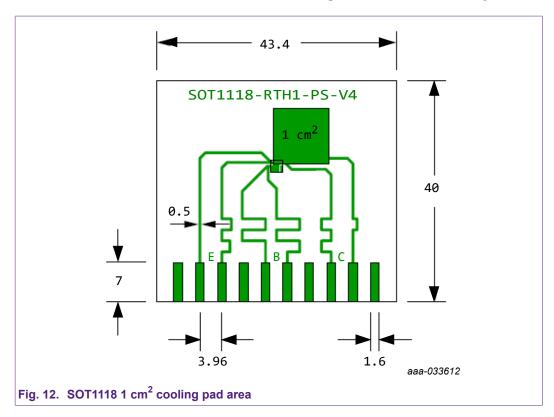

### 4.4. SOT1118

#### Thermal behavior of small-signal discretes on multilayer PCBs

Table 4. PBSM5240PF in SOT1118; typical values

| Sample              | Standard footprint    |                       | 1 cm <sup>2</sup> cooling pad |                       |

|---------------------|-----------------------|-----------------------|-------------------------------|-----------------------|

|                     | R <sub>th</sub> (K/W) | P <sub>tot</sub> (mW) | R <sub>th</sub> (K/W)         | P <sub>tot</sub> (mW) |

| 1                   | 149                   | 839                   | 82                            | 1524                  |

| 2                   | 154                   | 812                   | 86                            | 1453                  |

| 3                   | 153                   | 817                   | 81                            | 1543                  |

| Average             | 152                   | 822                   | 83                            | 1506                  |

| +15 % safety margin | 175                   | 715                   | 96                            | 1300                  |

| Single layer FR4    | 300                   | 410                   | 180                           | 700                   |

### 5. Conclusion

By using the additional copper area of multilayer PCB applications, power dissipation of a transistor can be increased significantly. Most improvement can be seen with newer flat or leadless packages, like SOT89 and SOT1061. The heat generated at the junction can be transported directly by conduction via the collector tab into the PCB. Most of the heat is transferred through the collector pad/exposed heatsink of SOT1061/SOT1118 packages to the PCB. Always consider the PCB as an additional tool to manage the thermal behavior of a transistor in any design.

### 6. Revision history

Table 5. Revision history

| Revision number | Date       | Description                                                        |

|-----------------|------------|--------------------------------------------------------------------|

| 2.0             | 2021-06-23 | Updated to use the latest Nexperia branding and legal disclaimers. |

| 1.0             | 2011-07-11 | Initial version                                                    |

#### Thermal behavior of small-signal discretes on multilayer PCBs

### 7. Legal information

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Thermal behavior of small-signal discretes on multilayer PCBs

## **List of Tables**

| Table 1. PBSS5350D in SOT457; typical values   | 6  |

|------------------------------------------------|----|

| Table 2. PBSS5330X in SOT89; typical values    |    |

| Table 3. PBSS5330PA in SOT1061; typical values | 9  |

| Table 4. PBSM5240PF in SOT1118; typical values | 10 |

| Table 5. Revision history                      | 10 |

## Thermal behavior of small-signal discretes on multilayer PCBs

# **List of Figures**

| Fig. 1. Typical structure of small signal packages | 2  |

|----------------------------------------------------|----|

| Fig. 2. Three heat transfer methods                | 3  |

| Fig. 3. Layer stack of modified Rth-PCBs           | 4  |

| Fig. 4. Layer 2, 3 and 4 cooling area              | 4  |

| Fig. 5. SOT457 standard footprint                  | 5  |

| Fig. 6. SOT457 1 cm2 cooling pad area              | 5  |

| Fig. 7. SOT89 standard footprint                   | 6  |

| Fig. 8. SOT89 1 cm2 cooling pad area               | 7  |

| Fig. 9. SOT1061 standard footprint                 | 8  |

| Fig. 10. SOT1061 1 cm2 cooling pad area            | 8  |

| Fig. 11. SOT1118 standard footprint                | 9  |

| Fig. 12. SOT1118 1 cm2 cooling pad area            | 10 |

### Thermal behavior of small-signal discretes on multilayer PCBs

## **Contents**

| 1. Introduction                                                         | 2        |

|-------------------------------------------------------------------------|----------|

| 2. Thermal resistance                                                   | 2        |

| 2.1. Key parameters                                                     | 2        |

| 2.1.1. Thermal resistance from junction to solder point                 | 2        |

| 2.1.2. Thermal resistance from junction to ambient R <sub>th(j-a)</sub> | 3        |

| 3. Heat transfer mechanism                                              |          |

| 3.1. Thermal conduction                                                 | 3        |

| 3.2. Thermal convection                                                 | 3        |

| 3.3. Thermal radiation                                                  | 3        |

| 4. Thermal measurement results                                          | 4        |

| 4.1. SOT457                                                             | 5        |

| 4.2. SOT89                                                              | 6        |

| 4.3. SOT1061                                                            | 8        |

| 4.4. SOT1118                                                            | <u>S</u> |

| 5. Conclusion                                                           | . 10     |

| 6. Revision history                                                     | 10       |

| 7. Legal information                                                    | 11       |

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 23 June 2021

<sup>©</sup> Nexperia B.V. 2021. All rights reserved