AN11243 Failure signature of electrical overstress on power MOSFETs Rev. 02 — 19 December 2017 Application not **Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | Power MOSFETs, Electrical Overstress (EOS), Unclamped Inductive Switching (UIS)                                                                                                                                                                                                                                                                                                                                                                                          |

| Abstract    | When Power MOSFETs fail, there is often extensive damage. Examination of the size and location of the burn mark, the failure signature, provides information about the type of fault condition which caused the failure. This document provides a catalogue of failure signatures from common electrical overstress failure modes. The catalogue can be used in forensic investigation of the underlying root cause of failure to improve module design and reliability. |

# nexperia

### **1** Introduction

Power MOSFETs are used to switch high voltages and currents, while minimizing their own internal power dissipation. Under fault conditions however, it is possible to apply voltage, current and power exceeding the MOSFET capability. Fault conditions can be either due to an electrical circuit failure or a mechanical fault with a load such as a seized motor. This leads to Electrical Overstress (EOS). Typically the consequence of EOS is the short circuiting of at least 2 of the 3 MOSFET terminals (gate, drain, source). In addition, high local power dissipation in the MOSFET leads to MOSFET damage which manifests as burn marks, die crack and in extreme cases as plastic encapsulation damage.

Examination of the size and location of the burn mark, the failure signature, provides information about the type of fault condition which caused the failure. Common fault conditions are:

- ElectroStatic Discharge (ESD)

- Unclamped Inductive Switching (UIS) commonly called Avalanche or Ruggedness

- Linear Mode operation

- Over-current

Packaged MOSFETs have been deliberately destroyed under these conditions. Images recorded of the ensuing burn marks on the silicon surface, provide a 'Rogue's Gallery' to aid the explanation of EOS failures.

<u>Section 1.1</u> to <u>Section 1.4</u> gives an overview of the common failure signatures.

Appendices in <u>Section 2.1</u> to <u>Section 2.17</u> provide further images.

### 1.1 ESD - Human body model

#### 1.1.1 EOS method

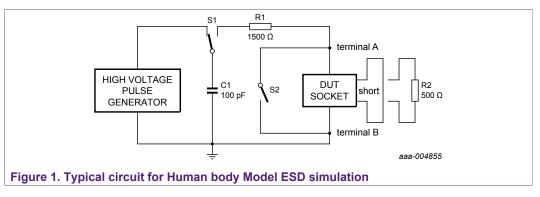

ESD pulses were applied using a standard Human-body Model ESD circuit; for details see *AEC* - *Q101* - *REV* - *May 15, 1996*. Voltage of the applied pulse was progressively increased until device failure was observed.

### 1.1.2 Fault condition simulated

Human body model ESD simulates situations when a voltage spike is applied to the MOSFET exceeding the maximum voltage that can be sustained by the gate oxide of either gate-source or gate-drain. The pulse is applied with 1500  $\Omega$  series resistance between the voltage origin and the MOSFET, which limits the rate of rise of the MOSFET gate voltage. Either human handling, electrical test equipment or malfunctioning circuits can easily apply such voltage pulses.

#### 1.1.3 Signature

Failure site is found in an edge cell of the MOSFET structure. Outer edge cells and cells near the gate are the first to be subjected to the incoming voltage pulse and are thus the first sites where the voltage exceeds the gate-oxide capability. The signature differs from Machine Model failures in that the fail site does not show such a strong tendency to group near the gate, due to the slower rise in gate voltage.

AN11243 Application note

### AN11243

#### Failure signature of electrical overstress on power MOSFETs

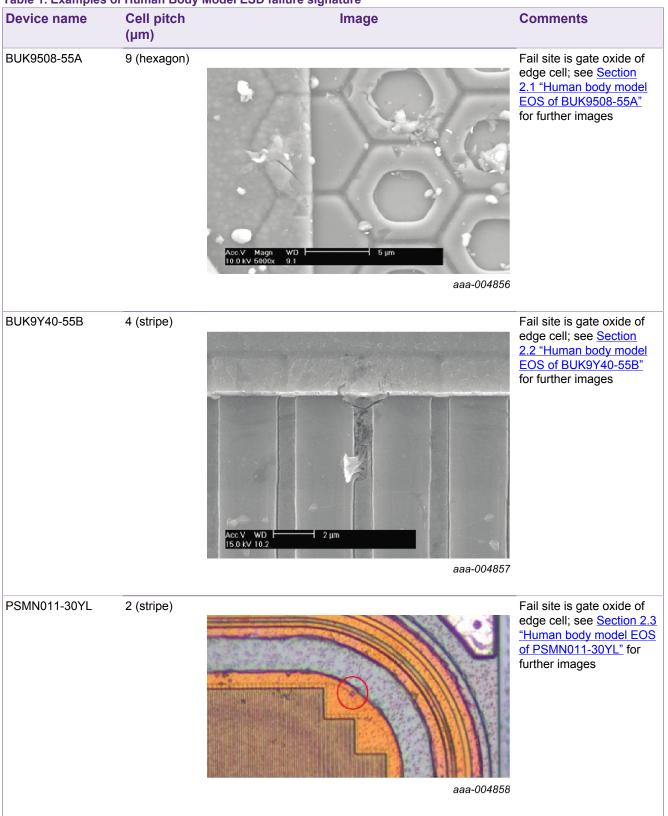

#### Table 1. Examples of Human Body Model ESD failure signature

AN11243 Application note © Nexperia B.V. 2017. All rights reserved.

## AN11243

| Device name    | Cell pitch<br>(µm) | Image | Comments                                                                                                                              |

|----------------|--------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

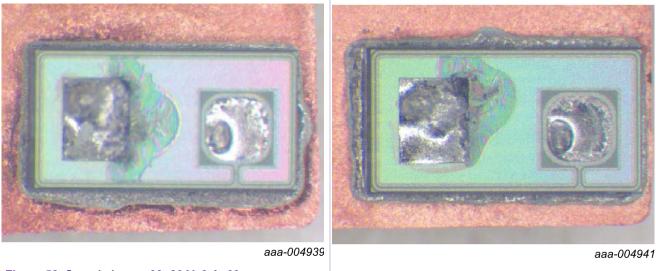

| PSMN8R5-100PSF | 2.5 (stripe)       |       | Fail site is gate oxide of<br>edge cell, see <u>Section 2.4</u><br>"Human body model EOS<br>of PSMN8R5-100PSF" for<br>further images. |

| BUK7Y3R0-40H   | 1.5 (stripe)       |       | Fail site is gate oxide of<br>edge cell, see <u>Section 2.5</u><br>"Human body model EOS<br>of BUK7Y3R0-40H" for<br>further images.   |

### 1.2 Unclamped Inductive Switching (UIS) (Avalanche or Ruggedness)

#### 1.2.1 EOS method

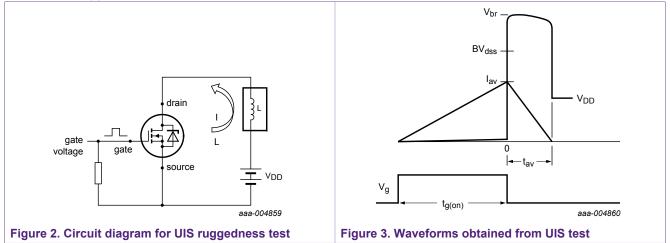

Inductive energy pulses were applied using a standard UIS circuit; for details see *AEC - Q101-004 - REV - May 15, 1996*. A fixed inductance value is selected. Current in the inductor prior to switching the MOSFET was progressively increased until device failure was observed.

Table 2. UIS ruggedness test circuit and waveforms

#### 1.2.2 Fault condition simulated

UIS simulates situations when a MOSFET is switched off in a circuit in which there is inductance. The inductance can be deliberate (such as an injector coil in a diesel engine system), or parasitic. As the current cannot decay to zero instantaneously through the inductance, the MOSFET source-drain voltage increases to take the device into avalanche breakdown. The energy stored in the inductance is then dissipated in the MOSFET.

#### 1.2.3 Signature

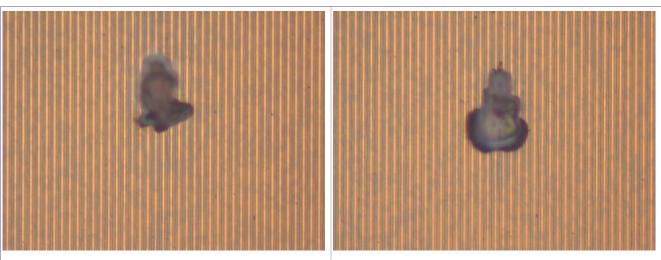

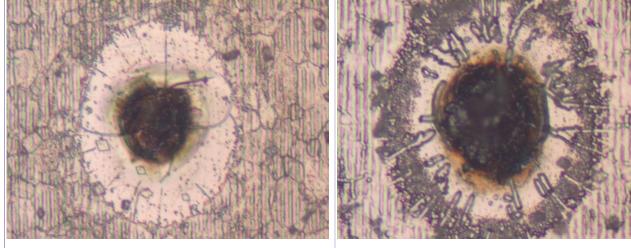

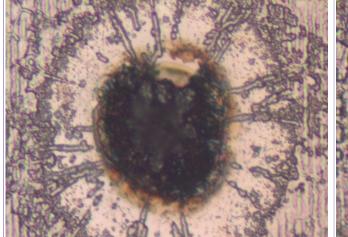

Failure site is found in an active MOSFET cell. The burn-mark is usually round in shape, indicating a central failure site and subsequent thermal damage.

If the avalanche event is long in duration (~ ms), then burn marks locate at central sites on the die, where there is maximum current flow and reduced heat dissipation. The sites are often adjacent to wire bonds/clip bonds where current density is high, but not directly under the wire bond/clip bond as it provides a local heat sink. Failure is at the hottest location of the die. For short avalanche events

For short avalanche events (~  $\mu$ s), the burn marks can take on more random locations over the die surface. The temperature rise in the chip is more uniform with negligible chance for current crowding and local heating on these time scales. For even shorter avalanche events, the burn marks can locate at die corners due to the discontinuity in cell structure at these locations.

## AN11243

### Failure signature of electrical overstress on power MOSFETs

| Device name   | Cell pitch<br>(µm) | Image                        | Comments                                                                                                                                                      |

|---------------|--------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUK7L06-34ARC | 9 (hexagon)        | <image/> <caption></caption> | round burn in active<br>area; see <u>Section 2.6</u><br><u>"Unclamped inductive</u><br><u>switching EOS of</u><br><u>BUK7L06-34ARC"</u> for<br>further images |

| BUK9Y40-55B   | 4 (stripe)         | <image/> <image/>            | round burn in active<br>area; see <u>Section 2.7</u><br><u>"Unclamped Inductive</u><br><u>Switching EOS of</u><br><u>BUK9Y40-55B</u> " for further<br>images  |

| PSMN7R0-30YL  | 2 (stripe)         | <image/> <image/>            | round burn in active<br>area; see <u>Section 2.8</u><br><u>"Unclamped inductive</u><br><u>switching EOS of</u><br><u>PSMN7R0-30YL"</u> for<br>further images  |

#### Table 2 Ex ad Inductivo Switching foilure cignot ofUnala

AN11243 **Application note**

## AN11243

| Device name    | Cell pitch<br>(µm) | Image | Comments                                                                                                                                                        |

|----------------|--------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

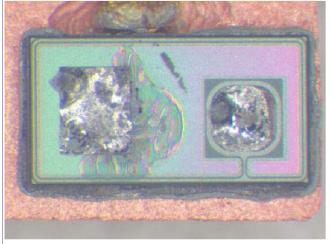

| PSMN8R5-100PSF | 2.5 (stripe)       |       | Round burn in active<br>area; see <u>Section 2.9</u><br><u>"Unclamped inductive</u><br><u>switching EOS of</u><br><u>PSMN8R5-100PSF"</u> for<br>further images. |

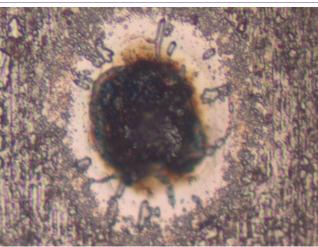

| BUK7Y3R0-40H   | 1.5 (stripe)       |       | Round burn in active<br>area; see <u>Section 2.10</u><br><u>"Unclamped inductive</u><br><u>switching EOS of</u><br><u>BUK7Y3R0-40H"</u> for<br>further images.  |

### 1.3 Linear mode operation

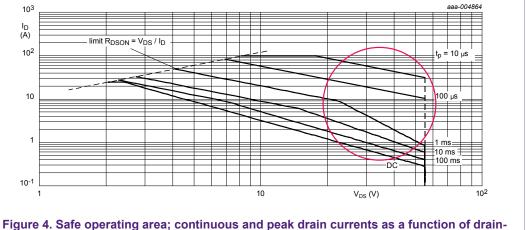

#### 1.3.1 EOS method

A Safe Operating Area (SOA) graph is included in all power MOSFET data sheets. Outside the defined safe region, the power dissipated in the FET cannot be removed, resulting in heating beyond the device capability and then device failure.

MOSFETs were taken and a fixed source-drain voltage applied. Current pulses of defined duration were applied and the current was increased until MOSFET failure was observed.

source voltage

### **1.3.2 Fault condition simulated**

Linear mode operation is common during device switching or clamped inductive switching and is not a fault condition unless the SOA is exceeded. Linear mode EOS simulates situations when a MOSFET is operated in Linear mode for too long. This situation can also occur if, when intending to turn the FET on, the gate signal voltage to the FET is too low. This condition can also arise when intending to hold the FET in the Off-state with high drain-source voltage. If the gate connection is lost, the gate voltage capacitively rises and the same Linear mode fault condition occurs

#### 1.3.3 Signature

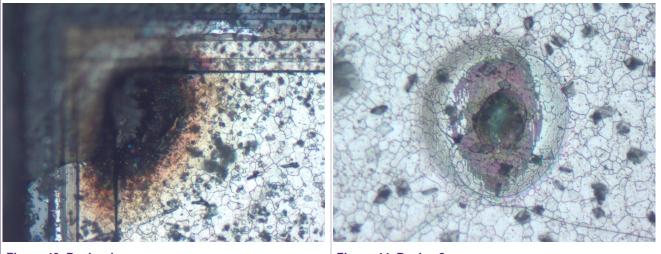

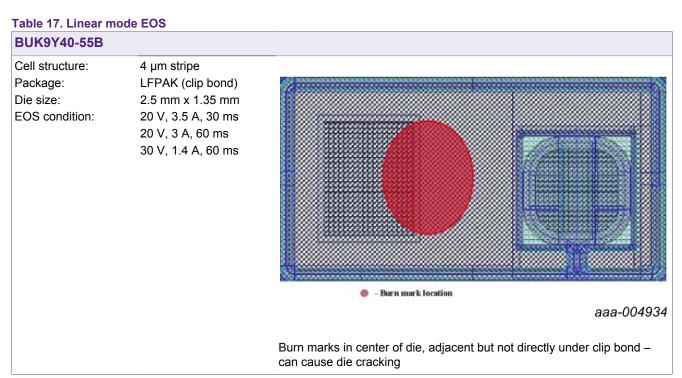

The hottest location of the die is a failure site that is usually at central sites on the die. The center of the die is where there is maximum current flow and reduced heat dissipation. The sites are often adjacent to wire bonds/clip bonds where current density is high, but not directly under the wire bond/clip bond as it provides a local heat sink.

### AN11243

### Failure signature of electrical overstress on power MOSFETs

#### Table 4. Examples of linear mode failure signature

| Device name   | Cell pitch<br>(µm) | Image             | Comments                                                                                                                                                           |

|---------------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUK7L06-34ARC | 9 (hexagon)        | <image/> <image/> | Burns located in center<br>of die adjacent to wire-<br>bonds; see <u>Section 2.11</u><br><u>"Linear mode EOS of</u><br><u>BUK7L06-34ARC"</u> for<br>further images |

| BUK9Y40-55B   | 4 (stripe)         | <image/> <image/> | Burn adjacent to location<br>of clip bond in center of<br>die; see Section 2.12<br>"Linear mode EOS of<br>BUK9Y40-55B" for further<br>images                       |

# AN11243

| Device name  | Cell pitch<br>(µm) | Image             | Comments                                                                                                                                                           |

|--------------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSMN7R0-30YL | 2 (stripe)         | <image/> <image/> | Burn adjacent to location<br>of clip bond in center of<br>die; see <u>Section 2.13</u><br><u>"Linear mode EOS of</u><br><u>PSMN7R0-30YL"</u> for<br>further images |

### AN11243

| Device name    | Cell pitch<br>(µm) | Image | Comments                                                                                                                                             |

|----------------|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

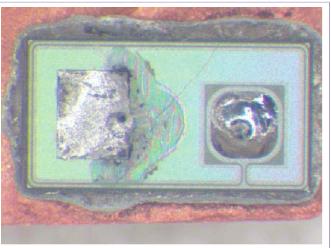

| PSMN8R5-100PSF | 2.5 (stripe)       |       | Burn between source<br>bond wires in active<br>area, see <u>Section 2.18</u><br>"Linear mode EOS of<br><u>PSMN8R5-100PSF"</u> for<br>further images. |

|                |                    |       |                                                                                                                                                      |

| BUK7Y3R0-40H   | 1.5 (stripe)       |       | Burn close to the source<br>clip location in the active<br>area, see Section 2.19<br>"Linear mode EOS of<br>BUK7Y3R0-40H" for<br>further images.     |

|                |                    |       |                                                                                                                                                      |

### 1.4 Over-current

#### 1.4.1 EOS method

The maximum current-handling capability is specified on the data sheet for Power MOSFETs. This capability is based on the current handling capability of wires or clips, before which fusing will onset, combined with the ability to dissipate heat. Exceeding this rating can result in catastrophic failure.

|                 |                    |                                                                         |     | $\frown$ |           |

|-----------------|--------------------|-------------------------------------------------------------------------|-----|----------|-----------|

| ID              | drain current      | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 100 °C; see Figure 1          | - / | 53       | A         |

|                 |                    | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 25 °C; see Figure 1           | -   | 76       | А         |

| I <sub>DM</sub> | peak drain current | $t_p \le 10 \ \mu s$ ; pulsed; $T_{mb} = 25 \ ^{\circ}C$ ; see Figure 3 | -   | 260      | A         |

|                 |                    |                                                                         |     | a        | aa-005071 |

Figure 5. Example of maximum current rating from the data sheet of PSMN7R0-30YL

### 1.4.2 Fault condition simulated

Over-current occurs if a FET is turned on with no element in the circuit to limit the current, resulting in a supply voltage being applied fully over the drain-source terminals of the FET. Typically this occurs if a load has been short-circuited. Alternatively if 2 FETs are operating in a half-bridge, over-current can ensue if both are turned on together.

#### 1.4.3 Signature

Failure site is initially where the current handling connections (wires or clips) meet the die. Normally damage is extensive however in over-current conditions, and spreads over the entire die surface with evidence of melted metallization and solder joints.

For wire-bonded packages, there is often evidence of fused wires. For clip-bonded packages, die crack is commonly observed.

### AN11243

### Failure signature of electrical overstress on power MOSFETs

#### Table 5. Examples of over-current failure signature

| Device name   | Cell pitch<br>(µm) | Image                                 | Comments                                                                                                                                                                                                                                   |

|---------------|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUK7L06-34ARC | 9 (hexagon)        | <image/> <image/>                     | Burns located in center<br>of die adjacent to wire-<br>bonds. Secondary<br>damage of remelted top<br>metal and solder die<br>attach; see <u>Section 2.14</u><br><u>"Over-current EOS of</u><br><u>BUK7L06-34ARC"</u> for<br>further images |

| PSMN7R0-30YL  | 2 (stripe)         | <image/> <image/> <caption></caption> | Burn adjacent to location<br>of clip bond in center of<br>die; see <u>Section 2.15</u><br><u>"Over-current EOS of</u><br><u>PSMN7R0-30YL"</u> for<br>further images                                                                        |

### 2 Appendices

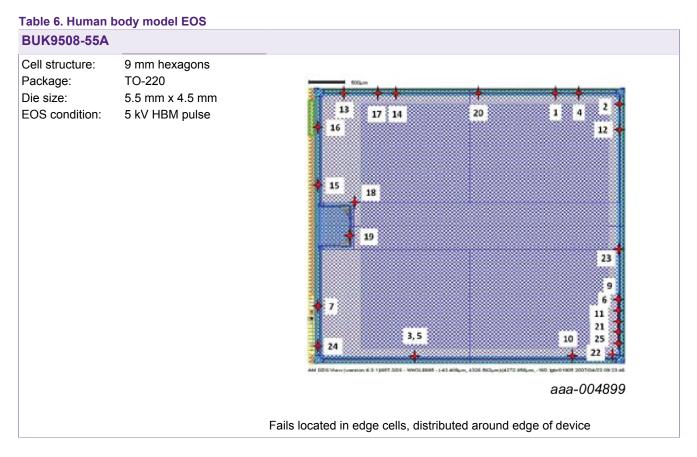

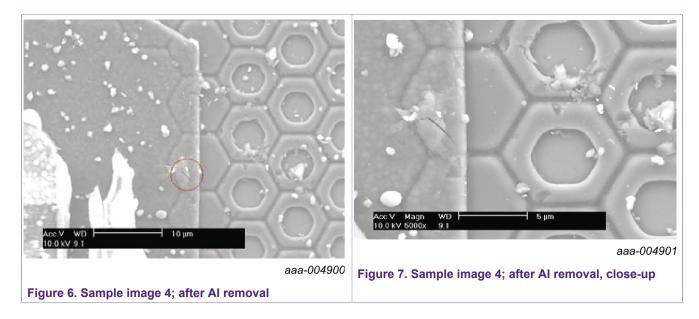

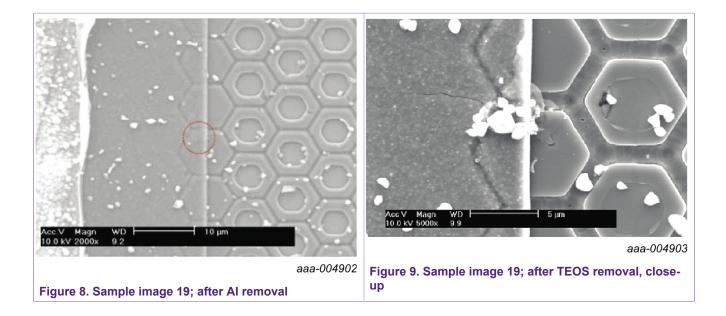

### 2.1 Human Body Model EOS of BUK9508-55A

### AN11243

Failure signature of electrical overstress on power MOSFETs

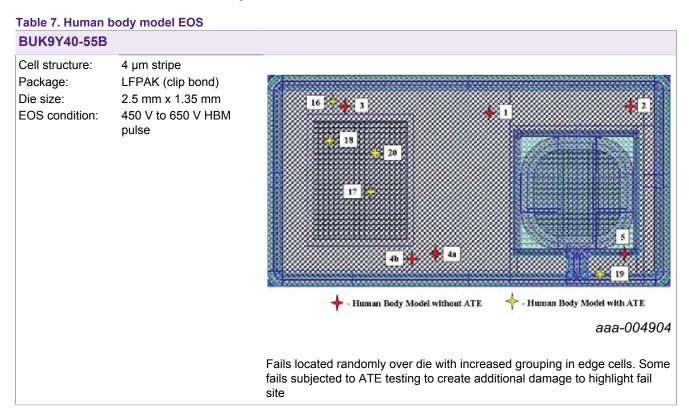

### 2.2 Human Body Model EOS of BUK9Y40-55B

Failure signature of electrical overstress on power MOSFETs

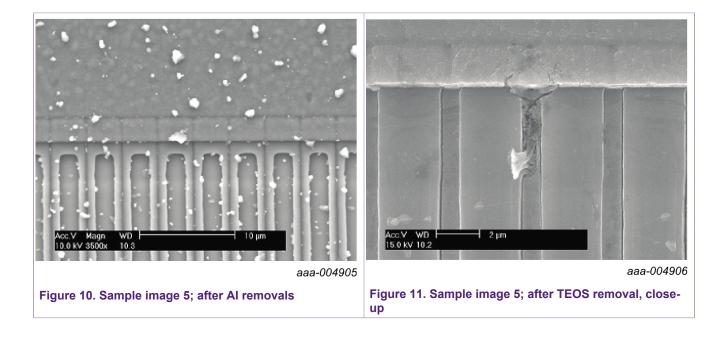

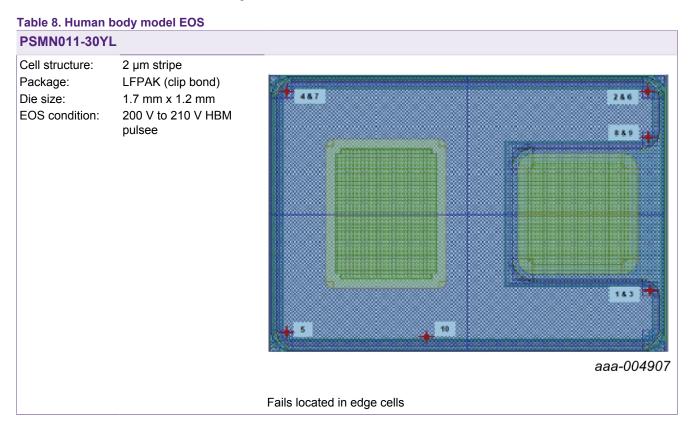

### 2.3 Human Body Model EOS of PSMN011-30YL

AN11243 Application note

#### Failure signature of electrical overstress on power MOSFETs

### 2.4 Human Body Model EOS of PSMN8R5-100PSF

| Table 9. Human | body | model | EOS |

|----------------|------|-------|-----|

| PSMN8R5-100    | PSF  |       |     |

| Cell structure: | 2.5 µm stripe                 |

|-----------------|-------------------------------|

| Package:        | SOT78                         |

| Die size:       | 4 mm x 2.67 mm                |

| EOS condition:  | 1.4 kV to 1.8 kV HBM<br>pulse |

|                 |                               |

### AN11243

Failure signature of electrical overstress on power MOSFETs

Figure 18. Device 5 after TEOS removal

Figure 19. Device 10 following decapsulation

Failure signature of electrical overstress on power MOSFETs

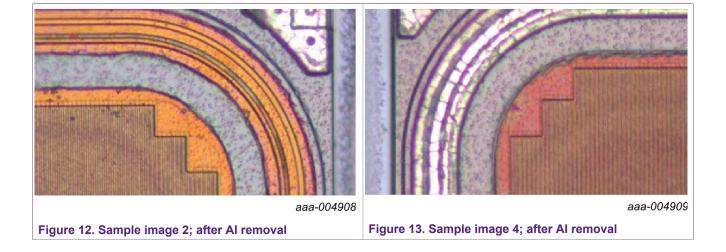

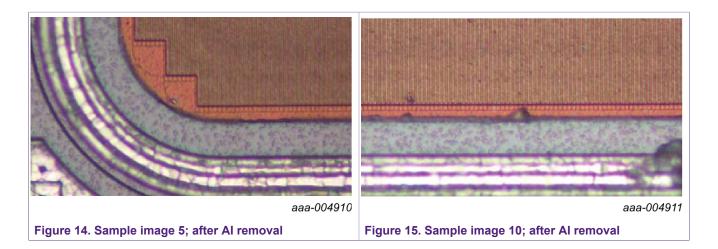

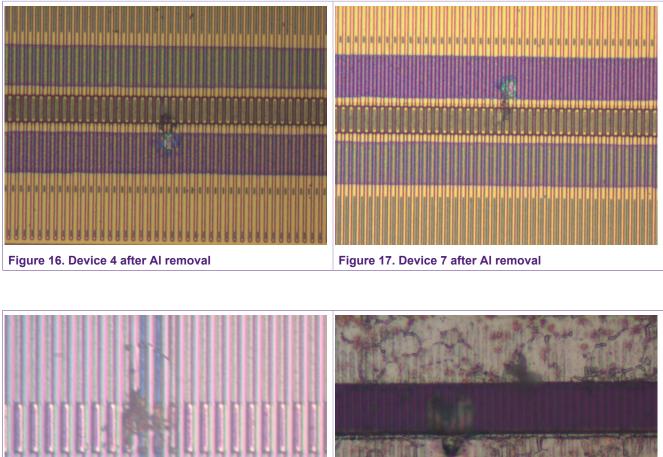

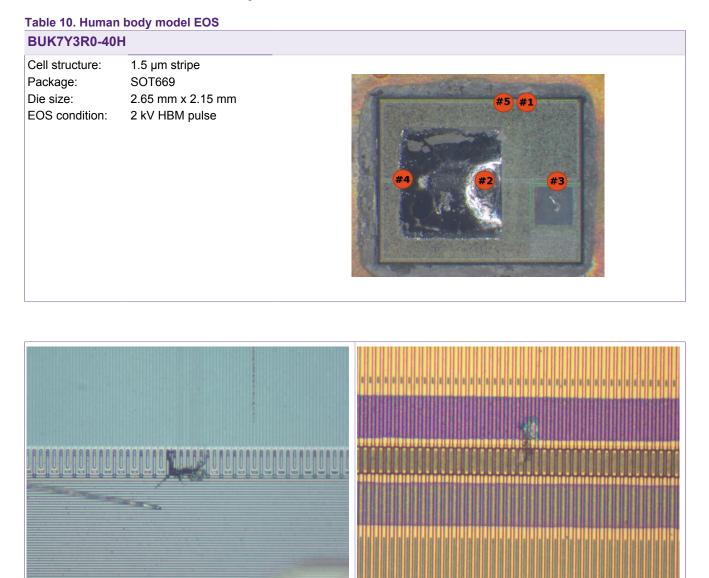

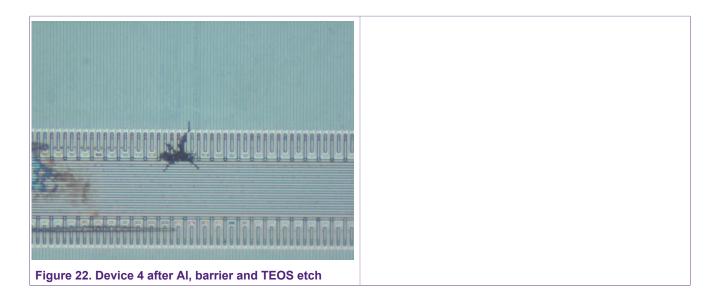

### 2.5 Human Body Model EOS of BUK7Y3R0-40H

Figure 20. Device 2 after AI, barrier and TEOS etch

Figure 21. Device 3 after AI, barrier and TEOS etch

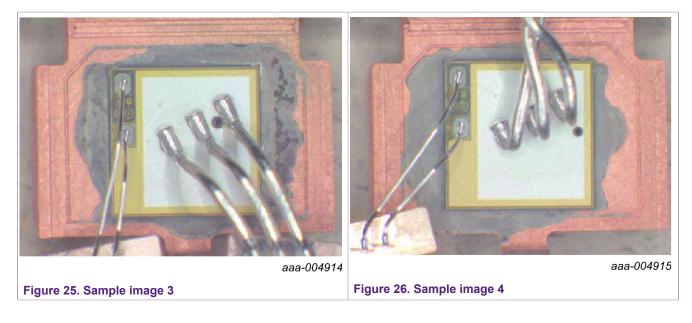

### 2.6 Unclamped Inductive Switching EOS of BUK7L06-34ARC

| Table 11. Unclamped BUK7L06-34ARC                          | inductive switchin                                                                    |                                                                                                           |

|------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Cell structure:<br>Package:<br>Die size:<br>EOS condition: | 9 mm hexagons<br>TO-220 (clip<br>bond)<br>4.3 mm x 4.3 mm<br>0.2 mH; 80 A to<br>110 A | Small round burn marks, randomly distributed over active area, close to but not directly under wire-bonds |

Figure 23. Sample image 1

Figure 24. Sample image 2

AN11243 Application note

aaa-004913

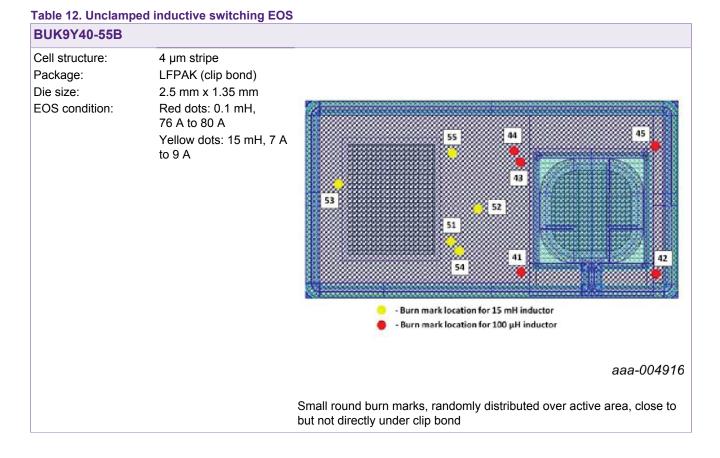

### 2.7 Unclamped Inductive Switching EOS of BUK9Y40-55B

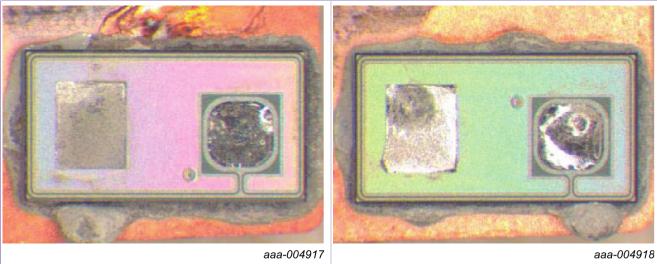

Figure 27. Sample image 41; 0.1 mH

Figure 28. Sample image 43; 0.1 mH

### Failure signature of electrical overstress on power MOSFETs

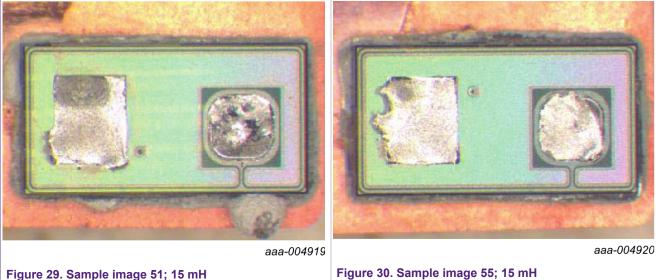

Figure 29. Sample image 51; 15 mH

#### Failure signature of electrical overstress on power MOSFETs

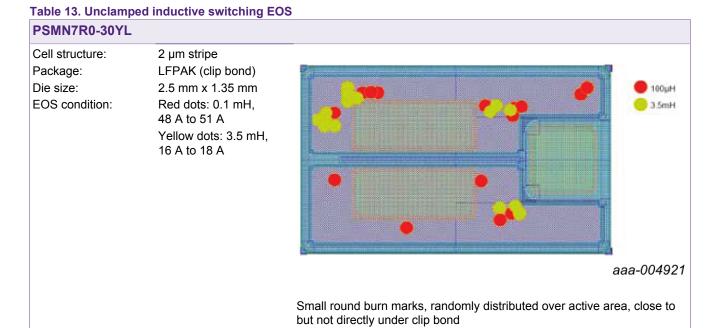

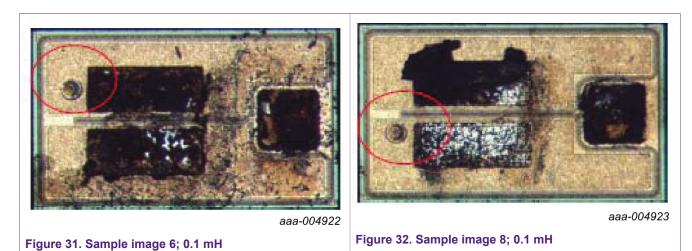

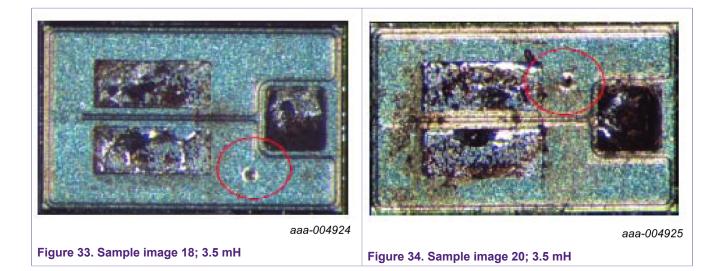

### 2.8 Unclamped Inductive Switching EOS of PSMN7R0-30YL

### AN11243

Failure signature of electrical overstress on power MOSFETs

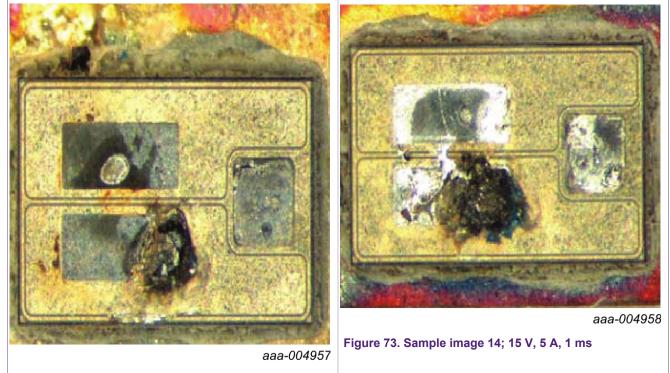

### 2.9 Unclamped Inductive Switching EOS of PSMN8R5-100PSF

| Table 14. | Unclamped | inductive | switching | EOS |

|-----------|-----------|-----------|-----------|-----|

|-----------|-----------|-----------|-----------|-----|

PSMN8R5-100PSF

Cell structure:

2.5 μm stripe

Package:

SOT78

Die size:

4 mm x 2.67 mm

EOS condition:

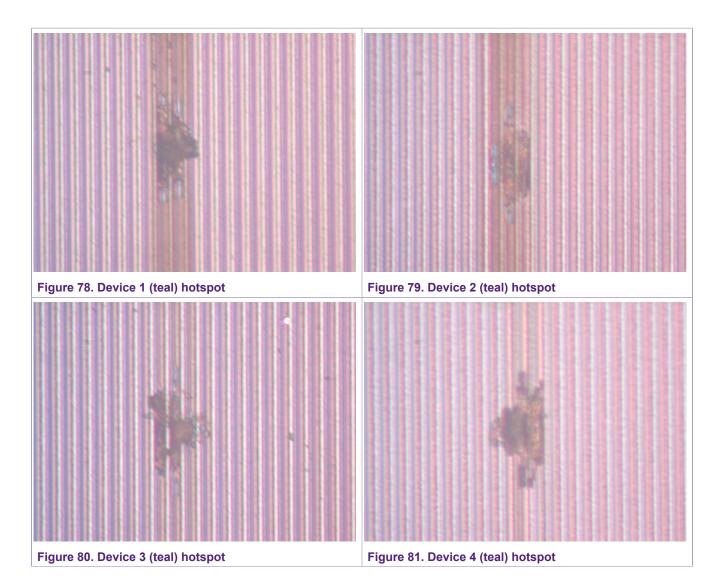

Teal dot – 25 mH

Orange dot – 100 uH

### AN11243

#### Failure signature of electrical overstress on power MOSFETs

Figure 35. Device 1 upper (orange) hotspot

Figure 36. Device 1 lower (orange) hotspot

Figure 37. Device 4 upper (orange) hotspot

Figure 38. Device 4 lower (orange) hotspot

### Failure signature of electrical overstress on power MOSFETs

Figure 39. Device 6 (teal) hotspot

Figure 40. Device 7 (teal) hotspot

Figure 41. Device 8 (teal) hotspot

Figure 42. Device 9 (teal) hotspot

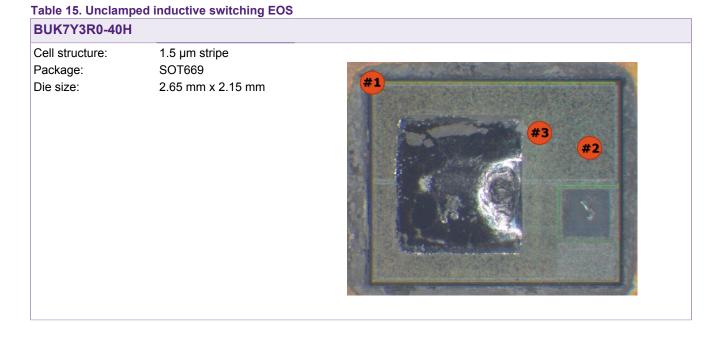

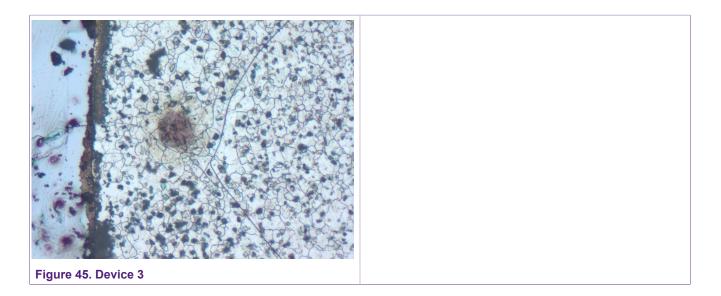

### 2.10 Unclamped Inductive Switching EOS of BUK7Y3R0-40H

#### Figure 43. Device 1

Figure 44. Device 2

### 2.11 Linear mode EOS of BUK7L06-34ARC

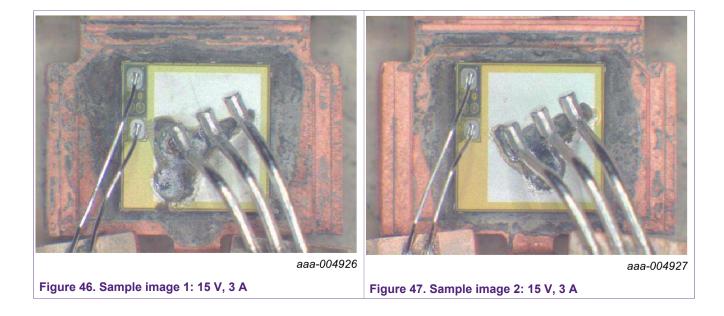

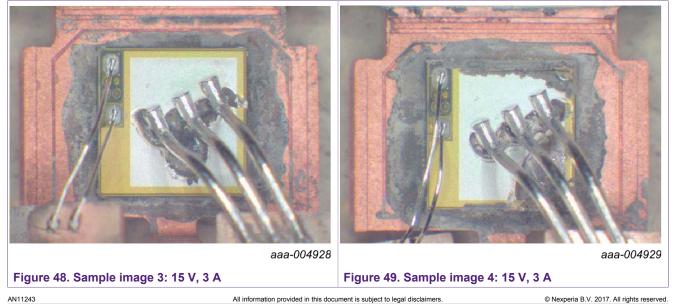

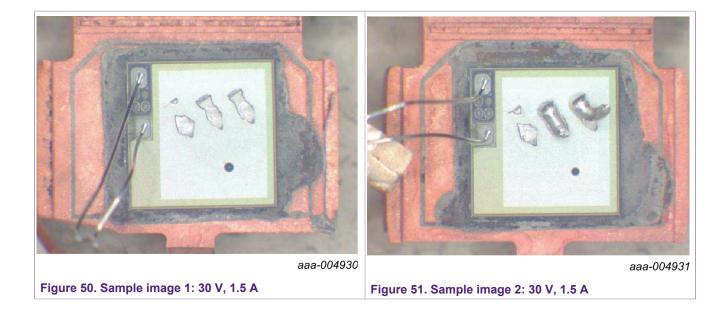

| Table 16. Linear mode EOS |                                                                          |  |  |  |

|---------------------------|--------------------------------------------------------------------------|--|--|--|

| BUK7L06-34AR              |                                                                          |  |  |  |

| Cell structure:           | 9 mm hexagon                                                             |  |  |  |

| Package:                  | TO-220 (clip bond)                                                       |  |  |  |

| Die size:                 | 4.3 mm x 4.3 mm                                                          |  |  |  |

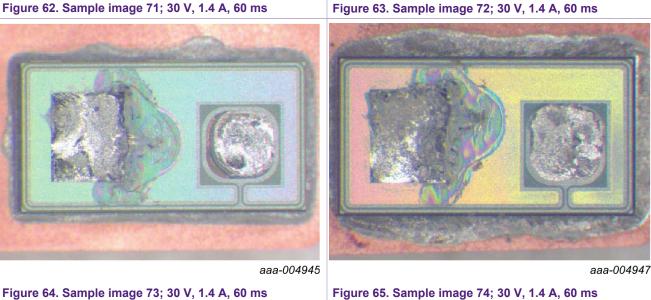

| EOS condition:            | 15 V, 3 A Burn marks located in middle of the die adjacent to wire bonds |  |  |  |

|                           | 30 V, 1.5 A Burn mark and location are more discrete at 20 V, 1.5 A      |  |  |  |

#### Failure signature of electrical overstress on power MOSFETs

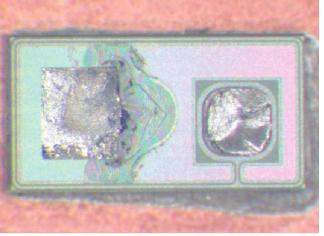

Figure 58. Sample image 66; 20 V, 3 A, 60 ms

Figure 59. Sample image 67; 20 V, 3 A, 60 ms

#### Failure signature of electrical overstress on power MOSFETs

aaa-004942

Figure 60. Sample image 68; 20 V, 3 A, 60 ms

aaa-004943

Figure 61. Sample image 69; 20 V, 3 A, 60 ms

aaa-004944

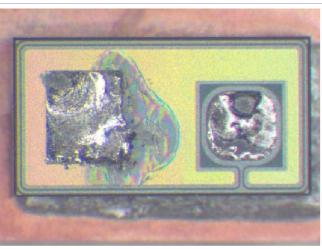

Figure 62. Sample image 71; 30 V, 1.4 A, 60 ms

aaa-004946

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2017. All rights reserved.

AN11243

Failure signature of electrical overstress on power MOSFETs

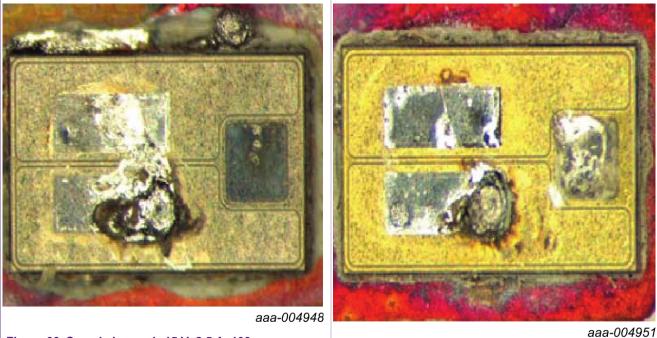

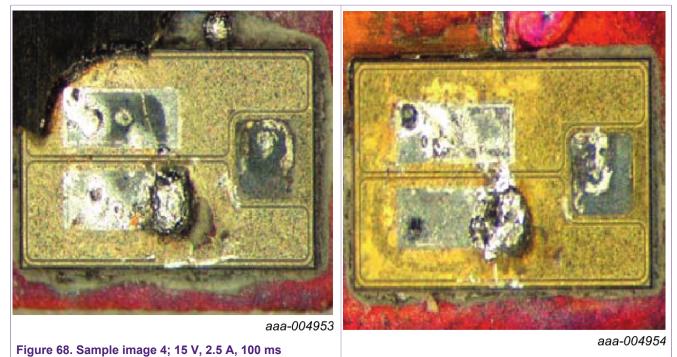

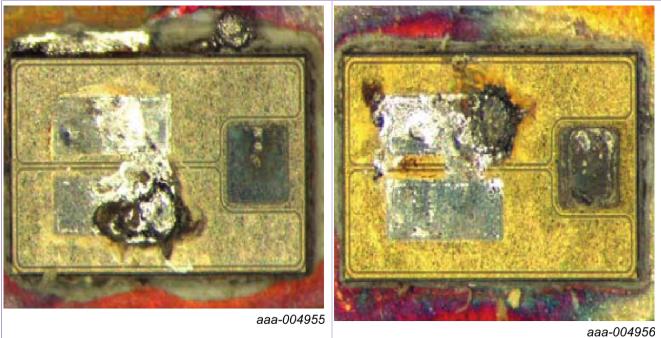

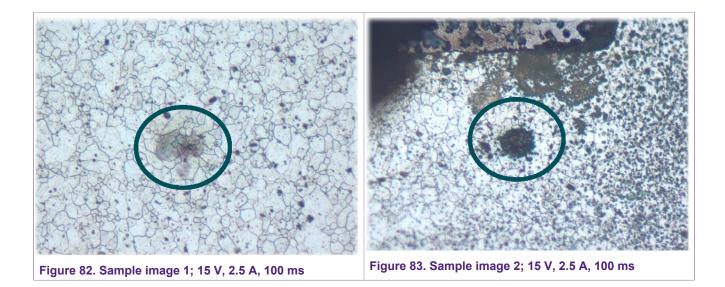

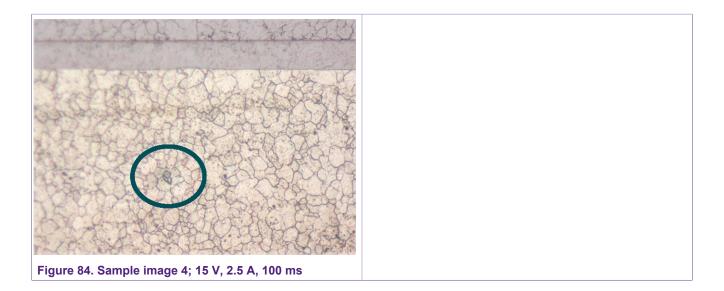

## 2.13 Linear mode EOS of PSMN7R0-30YL

| Table 18. Linear m<br>PSMN7R0-30YL |                                  |                                                                        |

|------------------------------------|----------------------------------|------------------------------------------------------------------------|

| Cell structure:<br>Package:        | 2 µm stripe<br>LFPAK (clip bond) | Burn marks in center of die, adjacent but not directly under clip bond |

| Die size:                          | 2.3 mm x 1.35 mm                 |                                                                        |

| EOS condition:                     | 0.1 mH, 48 A to 51 A             |                                                                        |

|                                    | 3.5 mH, 16 A to 18 A             |                                                                        |

Figure 66. Sample image 1; 15 V, 2.5 A, 100 ms

Figure 67. Sample image 2; 15 V, 2.5 A, 100 ms

### Failure signature of electrical overstress on power MOSFETs

Figure 69. Sample image 5; 15 V, 2.5 A, 100 ms

Figure 70. Sample image 11; 15 V, 5 A, 1 ms

Figure 71. Sample image 12; 15 V, 5 A, 1 ms

### Failure signature of electrical overstress on power MOSFETs

Figure 72. Sample image 13; 15 V, 5 A, 1 ms

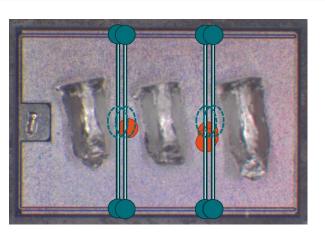

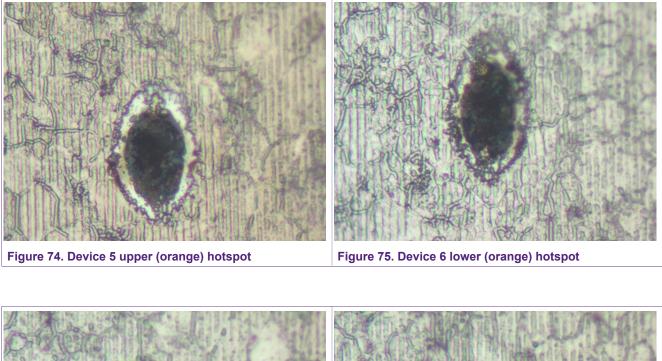

## 2.14 Linear mode EOS of PSMN8R5-100PSF

# Table 19. Linear mode EOS PSMN8R5-100PSF

| Cell structure: | 2.5 µn          |

|-----------------|-----------------|

| Package:        | SOT7            |

| Die size:       | 4 mm            |

| EOS condition:  | Teal d<br>pulse |

|                 | Orang<br>pulse  |

.5 μm stripe OT78 mm x 2.67 mm eal dot – 50 V 10 ms ulse length Drange dot – 70 V, 1 ms ulse length

Figure 77. Device 8 lower (orange) hotspot

## Nexperia

# AN11243

Failure signature of electrical overstress on power MOSFETs

### 2.15 Linear mode EOS of BUK7Y3R0-40H

| BUK7Y3R0-40H                                                               |                                                                                                        |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| BUK7Y3R0-40H<br>Cell structure:<br>Package:<br>Die size:<br>EOS condition: | 1.5 μm stripe<br>LFPAK (clip bond)<br>2.3 mm x 1.35 mm<br>0.1 mH, 48 A to 51 A<br>3.5 mH, 16 A to 18 A |  |

Burn marks in center of die, adjacent but not directly under clip bond

AN11243 Application note

Failure signature of electrical overstress on power MOSFETs

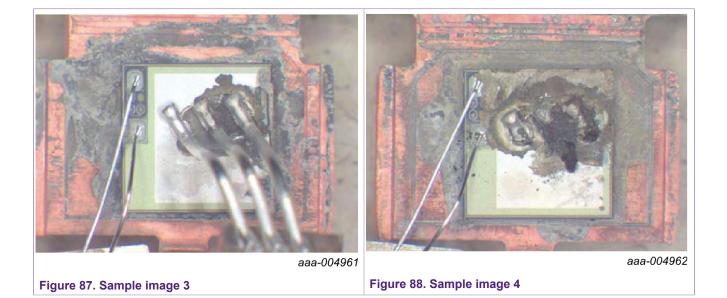

### 2.16 Over-current EOS of BUK7L06-34ARC

## Table 21. Over-current EOS

## BUK7L06-34ARC

#### Cell structure: Package: Die size: EOS condition:

9 mm hexagon TO-220 (clip bond) 4.3 mm x 4.3 mm 120 A

Extensive damage starting from die where wire bonds meet die.

Secondary damage of reflowed solder and even fused wires are visible

aaa-004959

Figure 85. Sample image 1

Figure 86. Sample image 2

Failure signature of electrical overstress on power MOSFETs

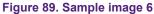

### 2.17 Over-current EOS of PSMN7R0-30YL

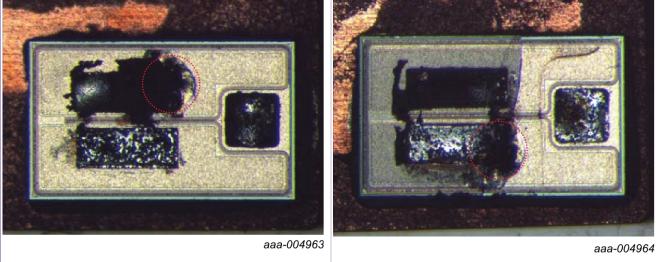

| PSMN7R0-30YL    |                   |                                                                        |

|-----------------|-------------------|------------------------------------------------------------------------|

| Cell structure: | 2 µm stripe       | Burn marks in center of die, adjacent but not directly under clip bond |

| Package:        | LFPAK (clip bond) | Some evidence of die-cracking.                                         |

| Die size:       | 2.3 mm x 1.35 mm  |                                                                        |

| EOS condition:  | 35 A, 35 ms       |                                                                        |

Figure 90. Sample image 7

Failure signature of electrical overstress on power MOSFETs

## 3 Abbreviations

| Table 23. Abbreviations |                               |

|-------------------------|-------------------------------|

| Acronym                 | Description                   |

| EOS                     | Electrical Overstress         |

| ESD                     | ElectroStatic Discharge       |

| UIS                     | Unclamped Inductive Switching |

# 4 Revision history

#### Table 24. Revision history

| Rev            | Date                                                                                       | Description       |

|----------------|--------------------------------------------------------------------------------------------|-------------------|

| 02             | 20171219                                                                                   | superseeds Rev 01 |

| Modifications: | <ul><li>Section ESD - Machine model removed</li><li>Additional EOS example added</li></ul> |                   |

| 01             | 20121029                                                                                   | first issue       |

#### Failure signature of electrical overstress on power MOSFETs

# 5 Legal information

### 5.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 5.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia. In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or

the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nexperia.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications, and (b) whenever customer (a) shall use the product for automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia's standard warranty and Nexperia's product claims beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Nexperia

# AN11243

Failure signature of electrical overstress on power MOSFETs

## **Tables**

| Tab. 1.  | Examples of Human Body Model ESD              |

|----------|-----------------------------------------------|

|          | failure signature4                            |

| Tab. 2.  | UIS ruggedness test circuit and waveforms 6   |

| Tab. 3.  | Examples of Unclamped Inductive Switching     |

|          | failure signature7                            |

| Tab. 4.  | Examples of linear mode failure signature 10  |

| Tab. 5.  | Examples of over-current failure signature 14 |

| Tab. 6.  | Human body model EOS                          |

| Tab. 7.  | Human body model EOS17                        |

| Tab. 8.  | Human body model EOS                          |

| Tab. 9.  | Human body model EOS 19                       |

| Tab. 10. | Human body model EOS                          |

| Tab. 11. | Unclamped inductive switching EOS23           |

# **Figures**

| Fig. 1.              | Typical circuit for Human body Model ESD simulation |  |

|----------------------|-----------------------------------------------------|--|

| Fig. 2.              | Circuit diagram for UIS ruggedness test             |  |

| Fig. 3.              | Waveforms obtained from UIS test                    |  |

| Fig. 4.              | Safe operating area; continuous and peak            |  |

| т ig. <del>т</del> . | drain currents as a function of drain-source        |  |

|                      | voltage9                                            |  |

| Fig. 5.              | Example of maximum current rating from the          |  |

| i ig. o.             | data sheet of PSMN7R0-30YL                          |  |

| Fig. 6.              | Sample image 4; after AI removal                    |  |

| Fig. 7.              | Sample image 4; after AI removal, close-up 15       |  |

| Fig. 8.              | Sample image 19; after AI removal                   |  |

| Fig. 9.              | Sample image 19; after TEOS removal,                |  |

|                      | close-up                                            |  |

| Fig. 10.             | Sample image 5; after AI removals                   |  |

| Fig. 11.             | Sample image 5; after TEOS removal, close-          |  |

|                      | up                                                  |  |

| Fig. 12.             | Sample image 2; after AI removal                    |  |

| Fig. 13.             | Sample image 4; after AI removal                    |  |

| Fig. 14.             | Sample image 5; after AI removal                    |  |

| Fig. 15.             | Sample image 10; after AI removal                   |  |

| Fig. 16.             | Device 4 after AI removal20                         |  |

| Fig. 17.             | Device 7 after Al removal20                         |  |

| Fig. 18.             | Device 5 after TEOS removal 20                      |  |

| Fig. 19.             | Device 10 following decapsulation                   |  |

| Fig. 20.             | Device 2 after AI, barrier and TEOS etch 21         |  |

| Fig. 21.             | Device 3 after AI, barrier and TEOS etch 21         |  |

| Fig. 22.             | Device 4 after AI, barrier and TEOS etch 22         |  |

| Fig. 23.             | Sample image 123                                    |  |

| Fig. 24.             | Sample image 2                                      |  |

| Fig. 25.             | Sample image 323                                    |  |

| Fig. 26.             | Sample image 4                                      |  |

| Fig. 27.             | Sample image 41; 0.1 mH                             |  |

| Fig. 28.             | Sample image 43; 0.1 mH                             |  |

| Fig. 29.             | Sample image 51; 15 mH25                            |  |

| Fig. 30.             | Sample image 55; 15 mH25                            |  |

| Fig. 31.             | Sample image 6; 0.1 mH                              |  |

| Fig. 32.             | Sample image 8; 0.1 mH                              |  |

| Fig. 33.             | Sample image 18; 3.5 mH 27                          |  |

| Tab. 12. | Unclamped inductive switching EOS | 24 |

|----------|-----------------------------------|----|

| Tab. 13. | Unclamped inductive switching EOS | 26 |

| Tab. 14. | Unclamped inductive switching EOS | 27 |

| Tab. 15. | Unclamped inductive switching EOS | 30 |

| Tab. 16. | Linear mode EOS                   | 32 |

| Tab. 17. | Linear mode EOS                   | 34 |

| Tab. 18. | Linear mode EOS                   | 37 |

| Tab. 19. | Linear mode EOS                   | 39 |

| Tab. 20. | Linear mode EOS                   | 42 |

| Tab. 21. | Over-current EOS                  | 44 |

| Tab. 22. | Over-current EOS                  | 45 |

| Tab. 23. | Abbreviations                     | 46 |

| Tab. 24. | Revision history                  | 46 |

|          |                                   |    |

| Fig. 34. | Sample image 20; 3.5 mH             |      |

|----------|-------------------------------------|------|

| Fig. 35. | Device 1 upper (orange) hotspot     | .28  |

| Fig. 36. | Device 1 lower (orange) hotspot     |      |

| Fig. 37. | Device 4 upper (orange) hotspot     | .28  |

| Fig. 38. | Device 4 lower (orange) hotspot     |      |

| Fig. 39. | Device 6 (teal) hotspot             | .29  |

| Fig. 40. | Device 7 (teal) hotspot             | .29  |

| Fig. 41. | Device 8 (teal) hotspot             | .29  |

| Fig. 42. | Device 9 (teal) hotspot             |      |

| Fig. 43. | Device 1                            | . 30 |

| Fig. 44. | Device 2                            | . 30 |

| Fig. 45. | Device 3                            |      |

| Fig. 46. | Sample image 1: 15 V, 3 A           | .32  |

| Fig. 47. | Sample image 2: 15 V, 3 A           | .32  |

| Fig. 48. | Sample image 3: 15 V, 3 A           |      |

| Fig. 49. | Sample image 4: 15 V, 3 A           | .32  |

| Fig. 50. | Sample image 1: 30 V, 1.5 A         | . 33 |

| Fig. 51. | Sample image 2: 30 V, 1.5 A         | . 33 |

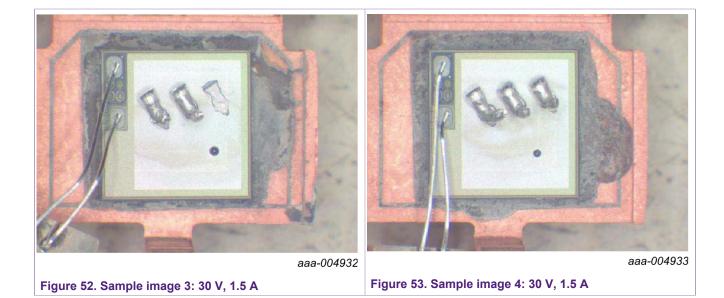

| Fig. 52. | Sample image 3: 30 V, 1.5 A         | . 33 |

| Fig. 53. | Sample image 4: 30 V, 1.5 A         | . 33 |

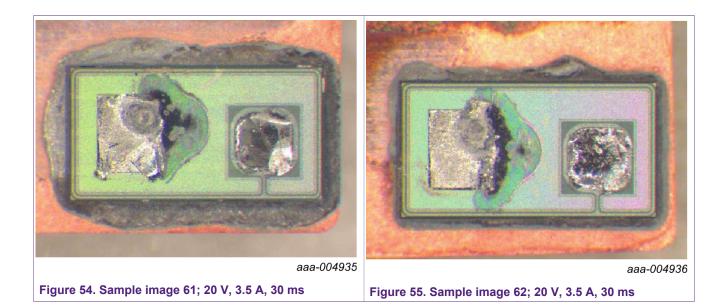

| Fig. 54. | Sample image 61; 20 V, 3.5 A, 30 ms | .34  |

| Fig. 55. | Sample image 62; 20 V, 3.5 A, 30 ms | .34  |

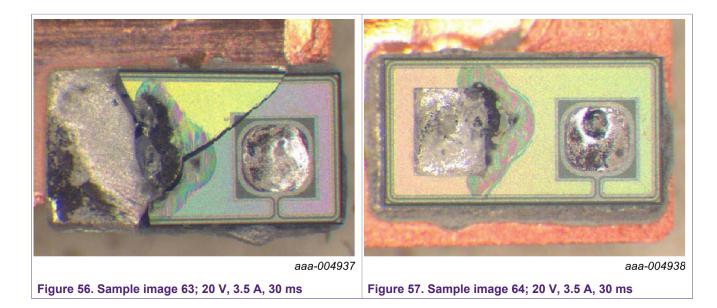

| Fig. 56. | Sample image 63; 20 V, 3.5 A, 30 ms |      |

| Fig. 57. | Sample image 64; 20 V, 3.5 A, 30 ms |      |

| Fig. 58. | Sample image 66; 20 V, 3 A, 60 ms   |      |

| Fig. 59. | Sample image 67; 20 V, 3 A, 60 ms   |      |

| Fig. 60. | Sample image 68; 20 V, 3 A, 60 ms   | 36   |

| Fig. 61. | Sample image 69; 20 V, 3 A, 60 ms   |      |

| Fig. 62. | Sample image 71; 30 V, 1.4 A, 60 ms |      |

| Fig. 63. | Sample image 72; 30 V, 1.4 A, 60 ms | .36  |

| Fig. 64. | Sample image 73; 30 V, 1.4 A, 60 ms | .36  |

| Fig. 65. | Sample image 74; 30 V, 1.4 A, 60 ms |      |

| Fig. 66. | Sample image 1; 15 V, 2.5 A, 100 ms | .37  |

| Fig. 67. | Sample image 2; 15 V, 2.5 A, 100 ms | .37  |

| Fig. 68. | Sample image 4; 15 V, 2.5 A, 100 ms | .38  |

| Fig. 69. | Sample image 5; 15 V, 2.5 A, 100 ms | .38  |

| Fig. 70. | Sample image 11; 15 V, 5 A, 1 ms    |      |

| Fig. 71. | Sample image 12; 15 V, 5 A, 1 ms    |      |

| Fig. 72. | Sample image 13; 15 V, 5 A, 1 ms    |      |

| 0        |                                     |      |

AN11243

© Nexperia B.V. 2017. All rights reserved.

| Fig. 73.<br>Fig. 74. | Sample image 14; 15 V, 5 A, 1 ms      | Fig. 83.<br>Fig. 84. | Sample image 2; 15 V, 2.5 A, 100 ms42<br>Sample image 4; 15 V, 2.5 A, 100 ms43 |

|----------------------|---------------------------------------|----------------------|--------------------------------------------------------------------------------|

| Fig. 75.             | Device 6 lower (orange) hotspot       | Fig. 85.             | Sample image 1                                                                 |

| Fig. 76.             | Device 7 upper (orange) hotspot40     | Fig. 86.             | Sample image 244                                                               |

| Fig. 77.             | Device 8 lower (orange) hotspot40     | Fig. 87.             | Sample image 344                                                               |

| Fig. 78.             | Device 1 (teal) hotspot41             | Fig. 88.             | Sample image 444                                                               |

| Fig. 79.             | Device 2 (teal) hotspot41             | Fig. 89.             |                                                                                |

| Fig. 80.             | Device 3 (teal) hotspot41             | Fig. 90.             | Sample image 745                                                               |

| Fig. 81.             | Device 4 (teal) hotspot41             | Fig. 91.             |                                                                                |

| Fig. 82.             | Sample image 1; 15 V, 2.5 A, 100 ms42 | Fig. 92.             | Sample image 945                                                               |

## Nexperia

# AN11243

### Failure signature of electrical overstress on power MOSFETs

### Contents

| 1         | Introduction                                      |     |

|-----------|---------------------------------------------------|-----|

| 1.1       | ESD - Human body model                            | 3   |

| 1.1.1     | EOS method                                        |     |

| 1.1.2     | Fault condition simulated                         | 3   |

| 1.1.3     | Signature                                         | 3   |

| 1.2       | Unclamped Inductive Switching (UIS)               |     |

|           | (Avalanche or Ruggedness)                         | 6   |

| 1.2.1     | EOS method                                        | 6   |

| 1.2.2     | Fault condition simulated                         |     |

| 1.2.3     | Signature                                         |     |

| 1.3       | Linear mode operation                             | 9   |

| 1.3.1     | EOS method                                        |     |

| 1.3.2     | Fault condition simulated                         | 9   |

| 1.3.3     | Signature                                         |     |

| 1.4       | Over-current                                      |     |

| 1.4.1     | EOS method                                        |     |

| 1.4.2     | Fault condition simulated                         |     |

| 1.4.3     | Signature                                         |     |

| 2         | Appendices                                        |     |

| 2.1       | Human Body Model EOS of BUK9508-55A               |     |

| 2.2       | Human Body Model EOS of BUK9Y40-55B               |     |

| 2.3       | Human Body Model EOS of PSMN011-30YL              | .18 |

| 2.4       | Human Body Model EOS of                           |     |

|           | PSMN8R5-100PSF                                    | .19 |

| 2.5       | Human Body Model EOS of BUK7Y3R0-40H              | 21  |

| 2.6       | Unclamped Inductive Switching EOS of              |     |

|           | BUK7L06-34ARC                                     | .23 |

| 2.7       | Unclamped Inductive Switching EOS of              |     |

| ~ ~       | BUK9Y40-55B                                       | .24 |

| 2.8       | Unclamped Inductive Switching EOS of              | ~~  |

| ~ ~       | PSMN7R0-30YL                                      | 26  |

| 2.9       | Unclamped Inductive Switching EOS of              | ~7  |

| 0.40      | PSMN8R5-100PSF                                    | .21 |

| 2.10      | Unclamped Inductive Switching EOS of BUK7Y3R0-40H | 20  |

| 2.11      | Linear mode EOS of BUK7L06-34ARC                  |     |

| 2.11      | Linear mode EOS of BUK9Y40-55B                    |     |

| 2.12      | Linear mode EOS of PSMN7R0-30YL                   |     |

| 2.13      | Linear mode EOS of PSMN47R0-301E                  |     |

| 2.14      | Linear mode EOS of BUK7Y3R0-40H                   |     |

| 2.15      | Over-current EOS of BUK7L06-34ARC                 |     |

| 2.10      | Over-current EOS of PSMN7R0-30YL                  |     |

| 2.17<br>3 | Abbreviations                                     |     |

| 3<br>4    | Revision history                                  |     |

| 4<br>5    | Legal information                                 |     |

| 5         | Leyai inivilliation                               | .4/ |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © Nexperia B.V. 2017.

#### All rights reserved.

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com

Date of release: 19 December 2017 Document identifier: AN11243