大電力アプリケーションにおけるパワーMOSFETの並列接続 改訂版1.1 - 2021年9月13日 アプリケーション・ノート

### ドキュメント情報

| 情報    | コンテンツ                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| キーワード | MOSFET, 並列使用, パラメータの個体差, シミュレーション                                                                                                                         |

| 概要    | 本アプリケーション・ノートでは並列接続されたMOSFET間の電流シェアリングの不均衡に対し、さまざまなパラメータがどのような影響を与えるかを検証します。また、パラメータの個体差を設計に盛り込む際のガイドラインを示します。信頼性と費用対効果に優れた大電力ソリューションの開発に役立つ実践的な説明も提供します。 |

大電力アプリケーションにおけるパワーMOSFETの並列接続

### 1. はじめに

今日の自動車産業や電力産業では大電力が求められるようになっており、低いオン抵抗(Roson)を必要とする設計が増えています。そうした設計は単一のMOSFETでは実現できず、複数のデバイスを並列使用する必要があります。大電力アプリケーションでは厚い銅箔のPCB、IMS(絶縁金属基板)、DBC(Direct Bonded Copper)、ベアダイなどの高性能基板が必要になります。並列使用することで、合計電流とそれに伴う電力損失が各デバイスで発生します。しかし、各デバイスの電力損失を知るにはキルヒホッフの電流則を適用すればよいという単純な話ではありません。MOSFETには個体差があるため、電流が均等に流れないという問題があるからです。

本アプリケーション・ノートでは並列接続されたMOSFET間で不均衡が生じるメカニズムを説明し、それを考慮するためのガイドラインとツールを提供します。最終的には並列接続された標準的なMOSFET (特定用途向けFET - ASFETを除く)を用いた回路設計に役立つベストプラクティスを提示します。

### 2. アプリケーション

並列接続されたMOSFETを必要とするアプリケーションはその動作に応じて「スイッチングモード」と「ロード・スイッチ」の2種類に大別されます。

スイッチングモードにはベルト・スターター・ジェネレーターやスーパーチャージャーなどのモーター・ドライブ・アプリケーション、ブレーキ回生システム、レギュレータ(DC/DC)やその他のインバータ(DC/AC)などのスイッチングモード・パワー・コンバータなどがあります。ここで、ハーフブリッジはすべての主要な回路トポロジーのベースとなる基本的な回路ブロックとなります。MOSFETは一定頻度でのON/OFFが必要ですが、その頻度はアプリケーションによって大きく異なります。また、MOSFETはシステムから負荷への出力を変調することを目的に、さまざまなデューティ・サイクルの矩形パルス(PWM)で駆動します。

ロード・スイッチングとは起動/安全スイッチ、電子ヒューズなど、主にMOSFETをバッテリと直列に接続して使用するアプリケーションのことを指し、バッテリ絶縁スイッチがその一例として挙げられます。MOSFETは一度スイッチをONにすると、システムのスイッチがOFFになるまで完全にONの状態を維持しなくてはなりません。ただし、回路の短絡など何らかの不具合が検出された場合のみ、直ちにOFFになることもあります。なお、このスイッチは逆接保護機能を追加するためにバック・トゥ・バック接続をする場合があります。

本アプリケーション・ノートでは主にスイッチングモード・アプリケーションとハーフブリッジ構成について説明します。

### 3. カギとなるスペック

注意すべき最も重要な数値はMOSFETのジャンクション温度です。ジャンクション温度は各デバイスにおける電力損失の関数であり、並列接続されたすべてのMOSFETで均一であることが理想です。 $P = V \times I$  であることから、並列接続されたすべてのMOSFETに同じ電圧がかかります。理想的な動作のためには各MOSFETで電流が均等に分配されるべきであり、これがMOSFETの性能を定量的に示す最もシンプルな指標となります。しかし、本アプリケーション・ノートの大部分で述べている消費エネルギー(電力)を考慮する方法も同様に有効です。

並列接続されたMOSFETの電流シェアリングに大きく影響するのはデータシートに記載されている $R_{DSon}$ 、 $Q_{G(tot)}$ 、 $V_{GS(th)}$ という3つのパラメータが部品間でばらついている場合です。これについては、後のセクションで詳しく説明します。

信頼性の高い設計を行うにあたり、設計段階で部品間の個体差がワーストケースにおける挙動を予測する方法を知っておくことが重要です。エレクトロニクスでは多くの側面で同じことが言えますが、最終的には設計者が前述のワーストケースにおいてどの程度の余裕を確保するかを決定しなければなりません。性能向上のために設計の堅牢性がある程度犠牲になる場合もあります。『The Art of Electronics(邦題:電子工学の作法)』ではこの点を以下についてもっと的確に表現しています。

「この例は設計者がよく直面するジレンマを物語っている。すなわち、ワーストケースを想定した設計基準を満たした保守的な回路で確実 に機能させる方法を選ぶか、ワーストケースの基準を満たさないが性能の高い回路設計でほぼ問題なく機能させる方法を選ぶかという2択 である。設計者は耳元で前者を選ぶべきだという小さな声を無視し、つい後者を選んでしまうことがある」。[1]

AN50005

大電力アプリケーションにおけるパワーMOSFETの並列接続

シミュレーションのセットアップ

免責事項: 本アプリケーション・ノートで記載している内容はSPICEモデルのカスタム案です。 実際にモデルをカスタマイズした後はユーザーが責任を持ってデータシートへの適合性を確認し てください。適合性は付録に記載されているガイドラインに従うことで確認できます。

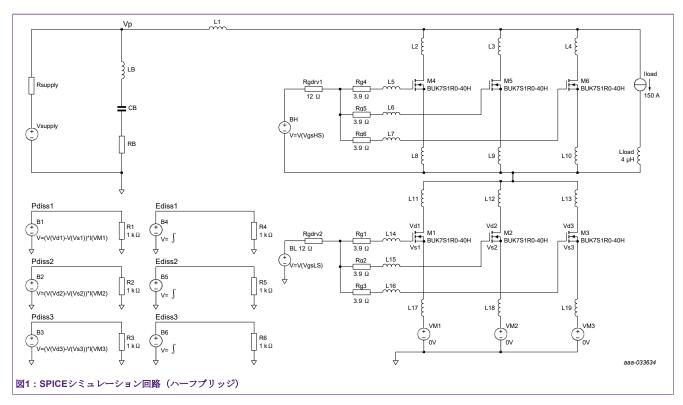

本アプリケーション・ノートで使用している回路は3つのMOSFETをハイサイドとローサイドで並列接続し、誘導性負荷を駆動する設計になっています(図1参照)。スイッチング周波数は20kHz、デューティ・サイクルは50%、最大Vesは15Vに設定されています。各MOSFETに流れる電流は50Aで、誘導性負荷と直列に使用される150Aの定電流源Iloadが設定されています。SPICEシミュレーションにはローサイドのMOSFETのソース経路に1つずつ、合計3つの0Vの電圧源VM1-VM3が使われています。これらの電圧源はローサイドのドレイン電流を測定しエネルギー/電力損失を算出するために使用されています。本書では特に断りのない限り、MOSFETはBUK7S1R0-40Hを使用しています。図1に示すように、このレイアウトに伴う寄生インダクタンスがシミュレーションに追加されています。3つに分岐した回路間で寄生インダクタンスに違いはありません(各分岐回路は1つのMOSFETと、そのインレット(電流の入口)とアウトレット(同出口)を並列で接続する経路、すなわち、ハイサイドではVsupplyとスイッチング・ノード、ローサイドではスイッチング・ノードとGNDに対応します)。

これは理想的なシナリオを想定したものですが、適切なマージンで実現可能です。この場合に発生する不均衡の原因はMOSFETの個体差のみです。レイアウトの重要性と寄生インダクタンスの影響については、後の章で詳しく説明します。

以降で示すガイドラインと考察はバッテリ電圧やその他の仕様に依存しません。さまざまなシナリオに応用可能です。

大電力アプリケーションにおけるパワーMOSFETの並列接続

### 4. MOSFETの損失とパラメータが電流シェアリングに与える影響

MOSFETの損失のメカニズムを理解し、それに影響を与える主なパラメータを明らかにすることで、ワーストケースの分析から、手間を減らしながらも現実的な評価結果を得ることができます。

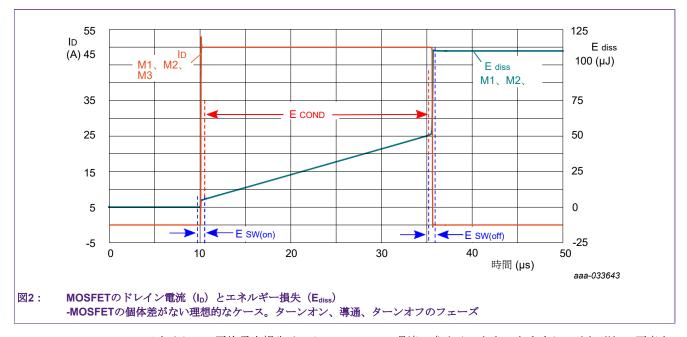

ハーフブリッジにおけるMOSFETの電力損失は導通とスイッチングの2つのプロセスで発生します。 図2に、理想的な場合の並列接続されたMOSFETに流れる電流と、そのエネルギー損失を示します。

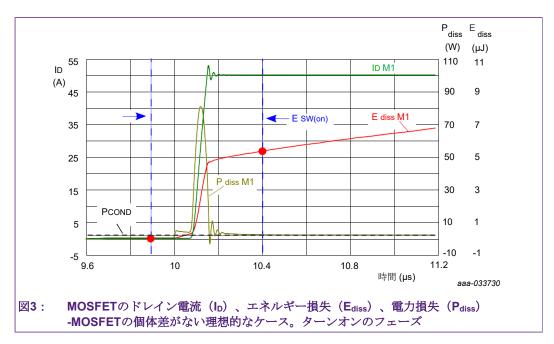

1サイクルの平均電力損失はシミュレーション環境で求めることもできますし、それぞれの要素を個別に考慮して算出することも可能です。スイッチング損失と導通損失は明確に分離しているわけではありません。しかしながら、シミュレーション環境においては電力損失がこの線引きに役立つことがあります。図3はターンオン・フェーズを示したもので、1つ目の点は電力が0Wになる約9.9  $\mu$  s、2つ目の点は損失電力が1.8Wでほぼ一定の約10.4  $\mu$  s(通電時の電力損失 $P_{cond}$ )にあります。なお、10  $\mu$  sから約10.1  $\mu$  sまでに見られる電力損失の増加はデバイスの電源ONに必要なゲート電荷によるものです。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

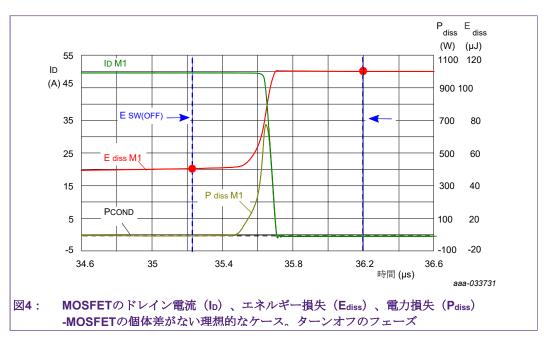

図4はターンオフ・フェーズを示したもので、1つ目の点は電力損失が1.8Wから上昇する約35.2 $\mu$  s、2つ目の点は電力が0Wになる約36.2 $\mu$  sにあります。

<u>式1</u>はMOSFETの電力損失を示し、<u>式2</u>と<u>式3</u>はスイッチングと導通による個々の損失を表しています。

$$Pavg(tot) = Psw + Pcond (1)$$

$$P_{SW} = (E_{SW(ON)} + E_{SW(OFF)}) \cdot f_{SW}$$

(2)

$$P_{cond} = E_{cond} \cdot f_{sw} \tag{3}$$

ここで、 $E_{sw(ON)}$ と $E_{sw(OFF)}$ はターンオン時、ターンオフ時におけるエネルギー損失、 $E_{cond}$ は1サイクル中の導通期間でのエネルギー損失、 $f_{sw}$ はスイッチング周波数です。この場合、 各MOSFETにおける1サイクルあたりの平均電力損失は20kHzで約2.1Wとなります。

AN50005

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

<u>表1</u>にスイッチング時(ON、OFFごと)と導通時におけるエネルギーの算定値を示します。各 MOSFETの分担度はさまざまな形で定義できます。ここでは<u>式4</u>を使用して、1つのMOSFETに おけるエネルギー損失と、並列接続された全デバイスにおけるエネルギー損失の合計との比とし て定義します。

全エネルギーシェアリング=

$$\frac{\left(E_{SW(ON)} + E_{SW(COND)}\right)_{(Mx)}}{\sum_{i=1}^{n} \left(E_{SW(ON)} + E_{SW(OFF)} + E_{SW(COND)}\right)_{(Mi)}} \bullet 100 \tag{4}$$

この場合、スイッチング(Esw(ON) + Esw(OFF))は損失全体の約55%を占めています。しかし、スイッチングと導通の損失比はスイッチング周波数に依存します。低い周波数では導通損失が、高い周波数ではスイッチング損失が支配的になります。したがって、評価を簡略化するためには最も影響が大きいパラメータのみを考慮してもよいでしょう。

MOSFETが完全にONの場合、損失をもたらすのはドレイン・ソース間のオン抵抗( $R_{DSon}$ )のみです。一方、スイッチングはスレショルド電圧( $V_{GS(th)}$ )と入力電荷( $Q_{G(tot)}$ )に依存します。

| デバイス | Esw(on) [µJ] | Esw(off) [µJ] | E <sub>COND</sub> [µJ] | 全シェアリン<br>グ |

|------|--------------|---------------|------------------------|-------------|

| M1   | 5.1          | 52.8          | 46.1                   | 33%         |

| M2   | 5.1          | 52.8          | 46.1                   | 33%         |

52.8

46.1

33%

表1: MOSFETの個体差がない理想的なケースのまとめ

5.1

М3

## 5. パラメータの個体差が電流シェアリングのパフォーマンスに与える影響

前述のように、製造におけるデータシート・パラメータの個体差は電流シェアリングに大きな影響を及ぼします。なお、個体差とはあるパラメータの最小値と最大値の差を指します。個体差はシリコン・ダイ製造時にウェハ内とウェハ間のばらつきによるものであり、避けられないものです。メーカーを問わず、すべてのMOSFETでこうした個体差が発生します。NexperiaのパワーMOSFETの製造プロセスでは優れた性能と信頼性を実現するために、個体差がなるべく小さくなるよう最適化されています。

並列接続されたデバイス間の電流シェアリングが、前述の各パラメータからどのような影響を受けるかを理解した上で、その対策とガイドラインを説明することが重要です。シミュレーション環境であれば、それを行うことが可能です。次のセクションではデータシート記載の個体差の最大値で各パラメータを設定します。ここで説明するシミュレーションの他に、付録には同じようなパラメータの個体差を持つMOSFETを用いた同一環境で取得した実測定データが記載されています。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 5.1. 静的な動作 (DC)

### 5.1.1. ドレイン・ソース間のオン抵抗R<sub>DSon</sub>

表2: データシート上のBUK7S1R0-40Hの特性 Roson

| 記号    | パラメータ | 条件                                                          | 最小値  | 代表値  | 最大値  | 単位         |

|-------|-------|-------------------------------------------------------------|------|------|------|------------|

| RDSon |       | $V_{GS}$ = 10 V; $I_{D}$ = 25 A; $T_{j}$ = 25 $^{\circ}$ C  | 0.62 | 0.88 | 1    | m $\Omega$ |

|       | のオン抵抗 | $V_{GS}$ = 10 V; $I_{D}$ = 25 A; $T_{j}$ = 105 $^{\circ}$ C | 0.87 | 1.3  | 1.6  | m $\Omega$ |

|       |       | $V_{GS}$ = 10 V; $I_{D}$ = 25 A; $T_{j}$ = 125 $^{\circ}$ C | 0.97 | 1.4  | 1.75 | m $\Omega$ |

|       |       | $V_{GS}$ = 10 V; $I_{D}$ = 25 A; $T_{j}$ = 175 $^{\circ}$ C | 1.2  | 1.8  | 2.2  | mΩ         |

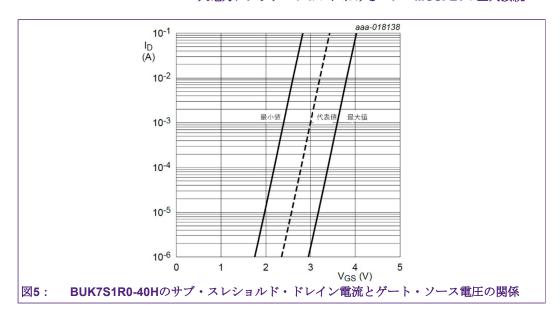

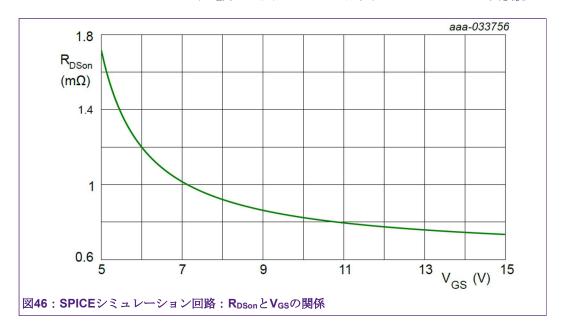

データシートによると、25° Cにおけるオン抵抗の個体差は $\Delta R_{DSon} = 0.38$ m $\Omega$ または $\Delta R_{DSon,rel} = \pm 21.6$ %(公称値に対する相対的な割合)になります。デバイスのSPICEモデルは $R_{DSon}$ の個体差を考慮して調整されています。調整はSPICEモデル内の「Drain, gate and source resistances」セクションにあるパラメータ $R_D$ の値を変更することで行います。{variable}の形式で変数を宣言した後、パラメータをスイープすることで適切な値を見つけることができます。

表3: Rpsonの個体差を求めるためのカスタム版SPICEモデル

| SPICEパラメータ-RD | R <sub>DSon</sub> [mΩ] | 条件                                             |

|---------------|------------------------|------------------------------------------------|

| 316.247u      | 0.62                   | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 25 A, |

| 576.260u      | 0.88                   | $T_j = 25$ ° C                                 |

| 695.949u      | 1.00                   |                                                |

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

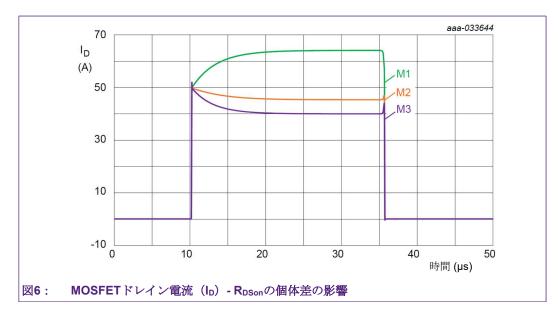

<u>表4</u>はシミュレーションの設定と結果をまとめたものです。 $R_{DSon}$ の低いMOSFET (M1) は多くのエネルギーを処理しなくてはならず、M3はその逆です。シェアリングへの影響は導通時とスイッチングの両方で発生します。M1の電力損失は2.5Wで、理想的なケース(2.1W)よりも20%程度多く、M3の電力損失は1.7Wでした。

この結果は最初の動作サイクルでのみ有効であり、その後のサイクルではRDpsonの温度依存性によって電流シェアリングがある程度均等化されます。詳しくは、温度依存性に関するセクションをご覧ください。

表4: Rosonの個体差による影響のまとめ

| デバイス | R <sub>DSon</sub> [mΩ] | Esw(on) [µJ] | Esw(off)<br>[µJ] | エネルギ<br>ーシェア<br>リ ン グ<br>(スイッ<br>チング) | Econd [µJ] | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|------------------------|--------------|------------------|---------------------------------------|------------|-----------------------------|

| M1   | 0.62                   | 5.0          | 65.9             | 40.7%                                 | 52.9       | 39.4%                       |

| M2   | 0.88                   | 5.1          | 48.8             | 30.9%                                 | 42.5       | 31.6%                       |

| М3   | 1                      | 5.1          | 44.3             | 28.4%                                 | 38.9       | 29.0%                       |

### 5.2. 動的な動作

### **5.2.1.** 全ゲート電荷-Q<sub>G(tot)</sub>

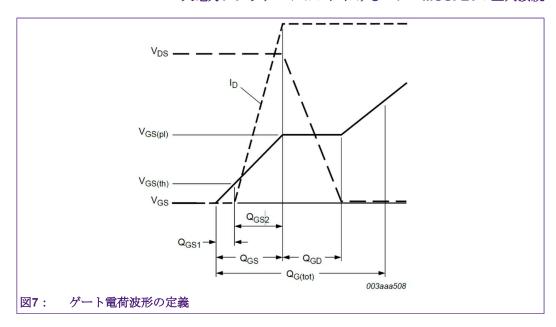

表5に、ゲート電荷パラメータ $Q_{G(tot)}$ 、 $Q_{GS}$ 、 $Q_{GD}$ の標準値と最大値を示します。パラメータの定義については図7を参照してください。

表5:BUK7S1R0-40Hのデータシート特性:ゲート電荷

| 記号      | パラメータ      | 条件                                                                    | 最小値 | 代表値 | 最大値 | 単位 |

|---------|------------|-----------------------------------------------------------------------|-----|-----|-----|----|

| QG(tot) | 全ゲート電荷     | I <sub>D</sub> = 25 A; V <sub>DS</sub> = 32 V; V <sub>GS</sub> = 10 V | -   | 98  | 137 | nC |

| Qgs     | ゲート・ソース電荷  |                                                                       | -   | 27  | 40  | nC |

| QGD     | ゲート・ドレイン電荷 |                                                                       | -   | 17  | 34  | nC |

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

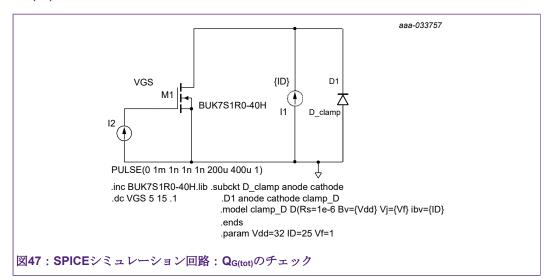

データシート上の個体差は $\Delta Q_{G(tot)}$  = 39 nCまたは $\Delta Q_{G(tot),rel}$  = +40 %となります。この個体差を SPICEモデルに適用するためには $C_{GS}$  と $C_{GD}$  を通じた $Q_{GS}$  と $Q_{GD}$  の影響を個別に評価する必要があります。

これを行うと、プラトー電圧以降の $V_{\rm cs}$ 曲線の傾きを制御することが難しくなるため、MOSFET の最大 $Q_{\rm G(tot)}$ がやや上昇します( $\underline{\boxtimes 7}$ 参照)。また、2つのキャパシタンスはほとんど独立しているため、必ずしも同じ挙動を示すとは限りません。たとえば、1つのMOSFETで $C_{\rm cp}$ が高め、 $C_{\rm cs}$ が低め、あるいはその中間になることもあり得えます。評価を容易にするため、両者は代表値と最大値のみ考慮するとします。

デバイスのSPICEモデルは $C_{GD}$ と $C_{GS}$ の個体差を考慮して調整されています。そのため、 $C_{GS}$ の値を変更し、 $C_{GD}$ の値に係数 $C_{GD}$ \_scale を乗じます。前者は定数です。 $C_{GD}$ は電圧依存値で、該当セクションの" $G_{GD}$ 132 VALUE …"の行で定義します。 $\{variable\}$ の形式で変数を宣言した後、パラメータをスイープすることで適切な値を見つけることができます。

表6: QG(tot)の個体差を求めるカスタム版SPICEモデル

| SPICEパラメータ |                      | 条件                                          |

|------------|----------------------|---------------------------------------------|

| CGS        | Q <sub>GS</sub> [nC] | V <sub>DS</sub> = 32 V;                     |

| 6.1n       | 27.148               | $I_D = 25 \text{ A}; V_{GS} = 10 \text{ V}$ |

| 9.24n      | 40.024               |                                             |

| CGD_scale  | Q <sub>GD</sub> [nC] |                                             |

| 0.84       | 17.008               |                                             |

| 1.65       | 34.211               |                                             |

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

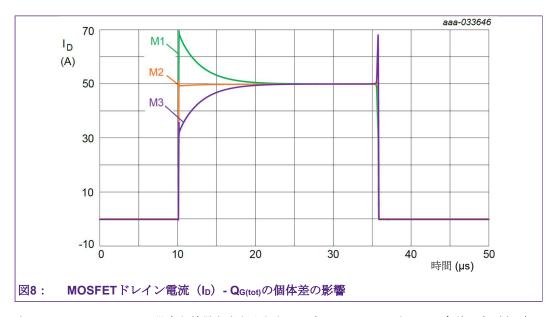

表7はシミュレーションの設定と結果をまとめたものです。QG(tot)はQGSとQGDの合計です(表6参照)。デバイスの電源をONにした時、まず入力容量の小さいデバイス(M1)のスイッチがONになるため、電流の大部分を受け持ちます。一方、MOSFETの電源をOFFにした時は、入力容量の大きいデバイス(M3)のスイッチが最後にOFFになるため、こちらが電流の大部分を受け持ちます。シェアリングの影響はスイッチング時が最も大きく、導通時の変化はわずかです。M3の損失電力は2.8W(理想的なケースよりも0.7W高い)、M1の損失電力は1.9Wでした。

表7:QG(tot)の個体差による影響のまとめ

| デバイス | QG(tot) [nC] | Esw(on) [µJ] | Esw(off)<br>[µJ] | エネルギ<br>ーシェア<br>リ ン グ<br>(スイッ<br>チング) | Econd [µJ] | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|--------------|--------------|------------------|---------------------------------------|------------|-----------------------------|

| M1   | 94.4         | 9.4          | 35.7             | 21.4%                                 | 49.9       | 35.8%                       |

| M2   | 125.7        | 6.9          | 60.8             | 31.9%                                 | 46.1       | 33.2%                       |

| М3   | 158.0        | 4.7          | 94.4             | 46.7%                                 | 43.2       | 31.0%                       |

#### **5.2.2.** ゲート・ソース間のスレショルド電圧 $-V_{GS(th)}$

表8: データシート上のBUK7S1R0-40Hの特性 VGS(th)

| • •     |           |                                                              |     |     |     |    |

|---------|-----------|--------------------------------------------------------------|-----|-----|-----|----|

| 記号      | パラメータ     | 条件                                                           | 最小値 | 代表値 | 最大値 | 単位 |

| VGS(th) | ゲート・ソース間の | $I_D$ = 1 mA; $V_{DS}$ = $V_{GS}$ ; $T_j$ = 25 $^{\circ}$ C  | 2.4 | 3   | 3.6 | V  |

|         | スレショルド電圧  | $I_D$ = 1 mA; $V_{DS}$ = $V_{GS}$ ; $T_j$ = 175 $^{\circ}$ C | 1   | -   | -   | V  |

|         |           | $I_D$ = 1 mA; $V_{DS}$ = $V_{GS}$ ; $T_j$ = -55 $^{\circ}$ C | -   | -   | 4.3 | V  |

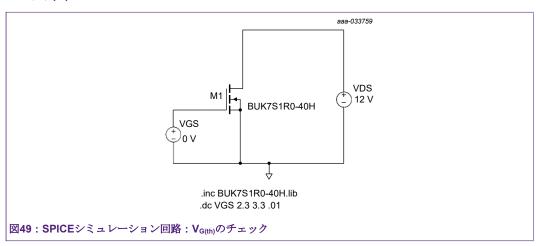

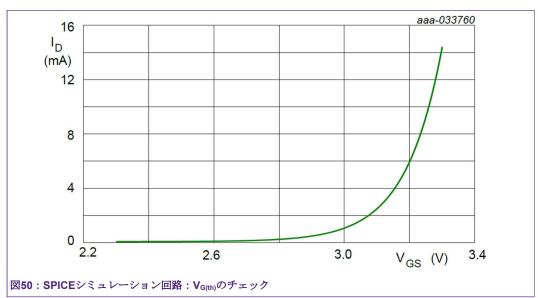

データシート上の個体差は $\Delta V_{GS(th)} = 1.2 \text{ V}$ または $\Delta V_{GS(th),rel} = \pm 20 \text{ %}$ となります。デバイスの SPICEモデルは $V_{GS(th)}$ の個体差を考慮して調整されています。調整は「.MODEL MINT NMOS」 セクションにあるパラメータ $V_{GS(th)}$ の値を変更することで行います。{variable}の形式で変数を宣言した後、パラメータをスイープすることで適切な値を見つけることができます。

表9: V<sub>GS(th)</sub>の個体差を求めるカスタム版SPICEモデル

| SPICEパラメータ-Vto | VGS(th) [V] | 条件                                            |

|----------------|-------------|-----------------------------------------------|

| 3.243          | 2.400       | V <sub>DS</sub> = 12 V, I <sub>D</sub> = 1 mA |

| 3.843          | 3.000       |                                               |

| 4.443          | 3.600       |                                               |

AN50005

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

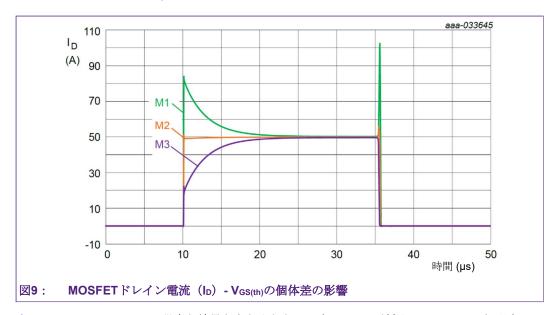

MOSFETのドレイン電流を<u>図9</u>に示します。回路にループ・インダクタンスが存在するため、電源 ONの後に電流が安定するのは $10 \mu$  s以降となります。詳細は「<u>レイアウト依存の寄生素子</u>」のセクションを参照してください。

表10はシミュレーションの設定と結果をまとめたものです。 $V_{\text{CS(th)}}$ が低めのMOSFETは処理するエネルギーが全般的に高くなります。電源をONにした時、まずM1のスイッチがONになるため、電流の大部分を受け持ちます。また、電源OFF時にM1は最後にOFFになるため、やはり大半の電流を処理することになります。スイッチング時は1つのMOSFET(M3)が回路動作に最小限でしか関与せず、導通の変化もわずかであるため、シェアリングの影響が最も大きくなります。M1の電力損失は4.7W(理想的なケースよりも2.6W高い)である一方、M3の電力損失はわずか1Wでした。

表10: VGS(th)の個体差による影響のまとめ

| デバイス | VGS(th) [V] | Esw(on) [µJ] | Esw(off) | エネルギ        | Econd [µJ] | エネルギー           |

|------|-------------|--------------|----------|-------------|------------|-----------------|

|      |             |              | [µJ]     | ーシェア        |            | シェアリン           |

|      |             |              |          | リング<br>(スイッ |            | ク<br>(導通)       |

|      |             |              |          | チング)        |            | \ \ <b>\</b> \\ |

| M1   | 2.4         | 9.3          | 172.2    | 74.4%       | 52.7       | 37.8%           |

| M2   | 3           | 5.1          | 48.7     | 22.1%       | 45.7       | 32.8%           |

| М3   | 3.6         | 2.2          | 6.4      | 3.5%        | 40.8       | 29.4%           |

結論として、 $V_{GS(th)}$ が低めのMOSFETは電源ONとOFFの両方でエネルギー処理量が大きくなりますが、キャパシタンスの個体差により、スイッチング時のエネルギーは複数デバイス間で均一化されます。 $V_{GS(th)}$ の温度依存性のため、この結果は最初の動作サイクルでのみ有効です。詳しくは該当の温度依存性セクションをご覧ください。スイッチング時と導通時の電流波形については図6、図8、図9、セクション7.1を参照してください。

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 5.3. 並列接続されたMOSFETと温度依存性

MOSFETは電気と熱のフィードバックループで構成されるシステムとして考えることができます (図10)。

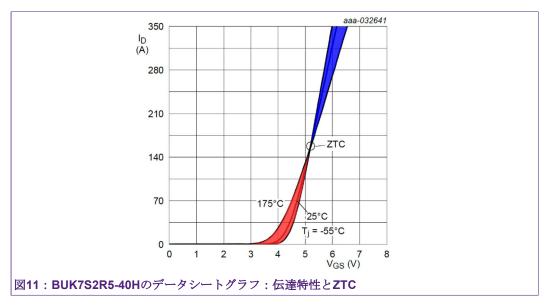

一般的に、パワーMOSFETはRDSOnの温度係数により、熱暴走を起こしにくいと考えられています。しかし、熱暴走を起こしにくいのはMOSFETが完全にONの状態の場合のみです。MOSFETがオン状態のとき、温度上昇に伴って2つの相反する要素が電流の振る舞いに影響を与えます。温度が上昇すると $V_{GS(th)}$ が低下するため、電流が増加します。一方、温度上昇に伴って $R_{DSOn}$ が増加し、電流を減少させます。ゲート・ソース間の電圧( $V_{GS}$ )が高くなると抵抗の増加が支配的になり、 $V_{GS}$ が低くなるとスレショルド電圧の低下が支配的になります。その結果、ある $V_{DS}$ に対して臨界 $V_{CS}$ のな存在することになります。この臨界値以下ではポジティブフィードバックが、臨界値以上ではネガティブフィードバックと熱的な安定性が発生します。この臨界点は $V_{CS}$ のに対してCZero Temperature Coefficient: ゼロ温度係数)と呼ばれます(図11参照)。

熱的サブシステムと電気的サブシステムの相互作用はNexperia Precision Electrothermal model (高精度電熱モデル)を用いてシミュレーションすることができます。このモデルではジャンクションとケース/マウントベースの2つのサーマルピンに追加でアクセスできます。これらのモデルを使用すると、並列接続に関するパラメータに温度依存性を含めることができるため、モデル化の精度が向上します。MOSFET、PCB、周囲からドレインタブまでを含めた熱システム全体をモデル化した回路をモデルのマウンティング・ベースピンに接続してください。

AN50005

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 5.3.1. 静的な動作 (DC) 時の温度依存性

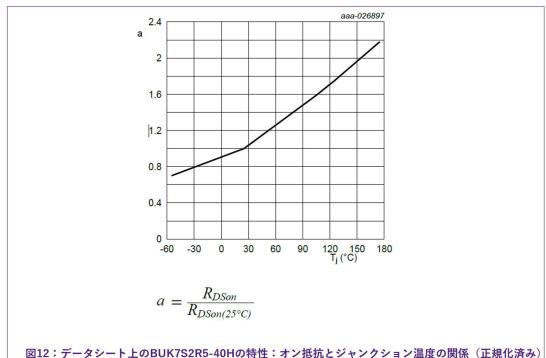

並列構成の場合、Rosonは正の温度係数 (PTC) を持つため、シェアリングを改善できるとい う利点があります(図12参照)。一方のMOSFETに流れる電流が増加して電力損失が大きく なると、Rosonも増加して導通が減少し、シェアリングが改善します。

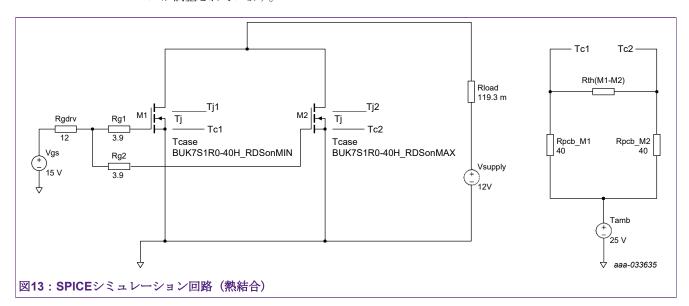

理想的なケースでは並列接続されたMOSFET間の熱結合が弱く、各MOSFETが周辺からの影響を 受けにくい場合、この現象が最も顕著になります。一方で、これは接合部の温度上昇にもつながり ます。この現象は定常状態でのシミュレーションで説明することができます(図13参照)。今回は 相互作用をシンプルにするため、並列接続するMOSFETは2つのみとします。さらに、2つの MOSFETとPCBとの接続部分の熱結合をモデル化するために、右側に示す第2の回路を使用します。

$\mathsf{M1}\mathcal{O}\mathsf{R}_{\mathsf{DSon}}$  (0.62  $\mathsf{m}\Omega$ ) が $\mathsf{M2}\mathcal{O}\mathsf{R}_{\mathsf{DSon}}$  (1 $\mathsf{m}\Omega$ ) よりも低くなるよう、デバイスの $\mathsf{SPICE}$ モデ ルが調整されています。

AN50005

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

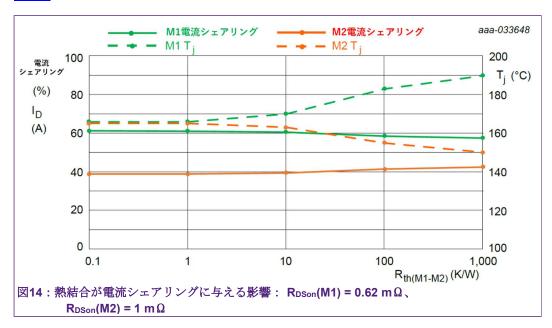

図14では2つのデバイスに流れる全電流を100Aとし、左側のY軸で電流とシェアリング (パーセント表示)を示しています。この例では純粋な定常導通を想定しているため、MOSFET間のシェアリングの度合いを計算するために電流を使用しています。2つのMOSFETの熱結合が悪化 (Rth(M1-M2)が上昇)すると、M1のジャンクション温度が上昇する一方、定常状態での電流シェアリングは改善されます(50%に近づきます)。また、熱的結合度が低い場合でも、Rosonの正の温度係数は電流シェアリングの改善方向にのみ作用します(各MOSFETにつき最大2%程度)。

### 5.3.2. 動的な動作時の温度依存性

スレショルド電圧は負の温度係数 (NTC) を持ち、ジャンクション温度が上昇すると減少するという特徴を持っています。並列接続されたMOSFETの場合、この特性は不利に働きます。たとえば、初期状態のジャンクション温度が高いデバイスではV<sub>GS(th)</sub>がさらに低下し、MOSFET内の電流が増加するため、電力損失も増加します。

静的な場合と同様、熱結合が良好ならMOSFETも同程度の温度に保たれます。並列接続された MOSFETの温度による勾配を緩和する方法について詳しくは「PCBレイアウトの影響:回路レイアウト」に別のガイドラインがあります。

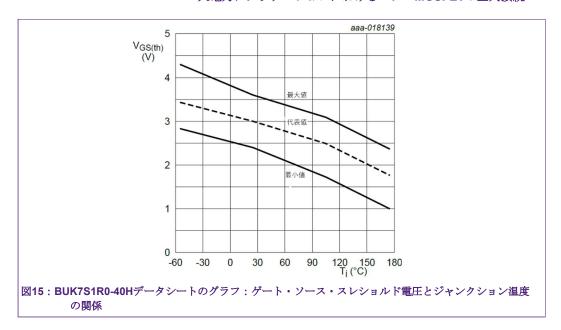

図15は $V_{GS(th)}$ の個体差がジャンクション温度に対してほぼ一定であることを示しています。ただし、この特性が確認されているのはドレイン電流が1mA時のみです。温度差が $20^{\circ}$ C( $25^{\circ}$ Cから $45^{\circ}$ C)になると、 $V_{GSth}$ は約0.2V低下します。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

最後に、RpsonやVcs(th)の場合とは異なり、入力電荷は温度によってわずかにしか変化しません。

### 5.4. データシートとロット間分散

MOSFETの複数並列接続を検討する際、データシート記載値の範囲はやや保守的であると考えるべきです。設計の信頼性は確実に上がりますが、ワーストケースを幅広く想定し堅牢性を向上させた分、結果的にコスト増につながることもあります。今回のケースの場合、データシートのように保証できないとしても、ワーストケースをさほど厳しく設定せず、十分現実的である設計が望ましいと考えられます。その際はロット間分散を考慮すべきです。

ロットとは同時期の生産工程で製造されたデバイスのグループを指します。ダイ自体の大きさにもよりますが、1つのロットに含まれるダイの数は数千から数百万以上に及びます。並列接続するMOSFETを選ぶ際、同じリールから製造されたパーツに注目すると、同ロットのデバイスが手に入る可能性が高まります。なお、基板に組み込む際はパッケージのマーキングコードの下段に記載されているロットコードが同一のMOSFETを選ぶとさらに絞り込めます。

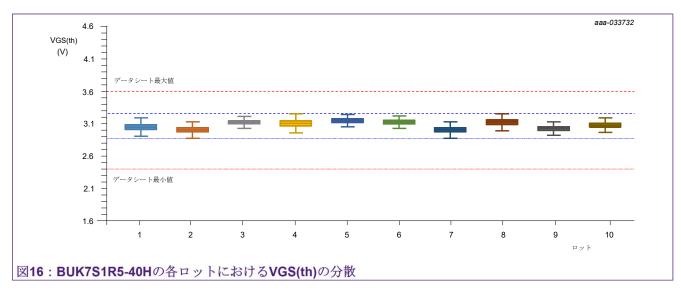

同一ロット内の個体差は、データシートに記載されている値よりもはるかに低いとされています。このことはさまざまなロットで通用します。図16は10種類のロットで生産されたBUK7S1R5-40Hの $V_{GS(th)}$ の個体差を示したものです。このケースでは2.86Vから3.28Vまで0.42V、6  $\sigma$  の分散が見つかりました。この値には少量の外れ値(図16ではプロットされていない)も考慮されています。したがって、測定されたワーストケースは  $\Delta V_{GS(th)}$  = 0.42 V or  $\Delta V_{GS(th),rel}$  =  $\pm$  7%であり、保証値(データシート値)の半分未満となります。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

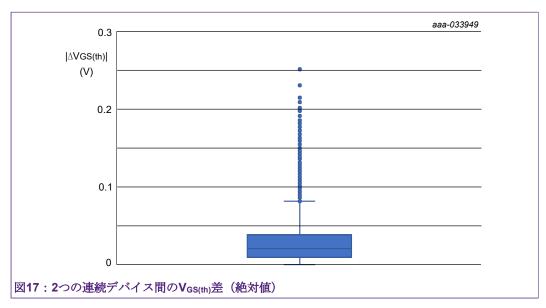

図17は別ロット内で連続する2つのデバイスにおける $V_{GS(th)}$ ( $|\Delta V_{GS(th)}|$ ) の差の絶対値を示したものです。この場合、 $6\sigma$ の分散が0.25V、すなわち $\Delta V_{GS(th),rel}$  =  $\pm 4\%$ と測定されました。そのため、同一リールからの連続した2つのMOSFETを並列接続した場合、 $V_{GS(th)}$ の差は複数ロット間での差よりもさらに小さくなります。

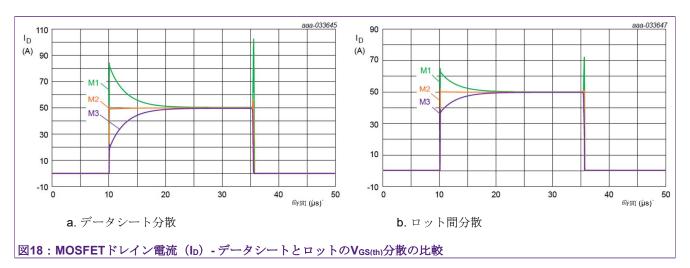

図18はMOSFETのドレイン電流を $V_{GS(th)}$ がデータシートのワーストケースとロット間の差の場合で比較したものです。表11には各MOSFETのエネルギーシェアリングが記載されています。M1の電力損失は合計2.8W、M3は1.5Wです。したがって、 $V_{GS(th)}$ が±7%異なると、M1の1サイクルで1.9W減少するため、この2つのMOSFETの間の損失の比率は約5対1から2.5対1に減少します。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

表11: VGS(th)のロット間分散の影響のまとめ

| P + | 2 1 1/420 100 1 | AF E     |       |            |                |

|-----|-----------------|----------|-------|------------|----------------|

| デバイ | VGS(th) [V]     | Esw [µJ] | エネルギ  | Econd [µJ] | エネルギー<br>シェアリン |

| ス   |                 |          | ーシェア  |            | シェアリン          |

|     |                 |          | リング   |            | グ              |

|     |                 |          | (スイッ  |            | (導通)           |

|     |                 |          | チング)  |            |                |

| M1  | 2.79            | 97.0     | 51.3% | 48.7       | 35.6%          |

| M2  | 3               | 59.4     | 31.4% | 45.4       | 33.2%          |

| M3  | 3.21            | 32.6     | 17.2% | 42.7       | 31.2%          |

|     |                 |          |       |            |                |

### 6. 回路の最適化

回路のアレンジは大きく分けて2種類あり、それぞれ電流シェアリングに及ぼす影響が異なります。 アレンジの対象の1つ目はゲート抵抗の分割、2つ目はMOSFETのソース経路の素子です。

### 6.1. ゲート抵抗の分割

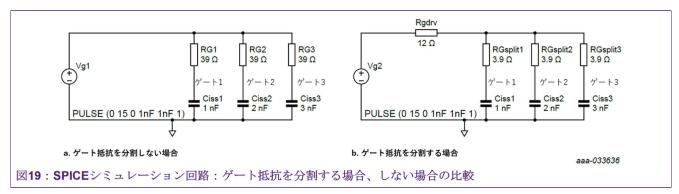

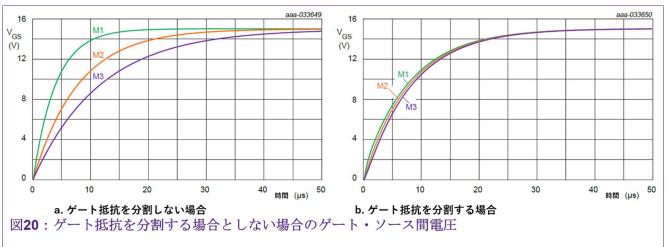

1つ目の回路アレンジは大きな欠点がなく、実装がシンプルであるという大きな利点があります。図18 bに示すように、このアレンジではゲート抵抗を各MOSFETのゲートに近い抵抗とドライバ側の共有抵抗に分けます。そうすることにより、個体差の影響の低減と主にスイッチング時のシェアリングの改善が実現し、しかも導通時の影響はほとんどありません。

MOSFETゲート間の結合を最大限に高めるには、分割した抵抗の値をできるだけ低くすることが重要です。そうすることにより、入力キャパシタンスが事実上並列化されていると考えることができます。この効果は簡単にシミュレーションで確認することができます。各MOSFETのドライバと入力インピーダンスをモデル化した2つの回路を比較すれば、それが可能です。図19aは各MOSFETのゲートの制御電圧を示しています。Cissが大きいMOSFETの場合はこの電圧の立ち上がりが鈍化し、逆にキャパシタンスが小さい場合は鈍化が少なくなります。

ゲート抵抗を分割することで、各ゲートの制御電圧の差は無視できるほど小さくなります(図 19 b)。図19のSPICE回路に使われている名称を使うと、ドライバのゲート抵抗は次のように算出できます。

$$R_{G,drv} = \frac{R_G}{nFET} - \frac{R_{G,split}}{nFET}$$

(5)

RG,drvの値は四捨五入して12 $\Omega$ としています。RG,drvを小さくすることで、不均等なシェアリングが発生するスイッチング時間を短縮することができます。同様にRG,splitを小さくするほどMOSFETのゲート結合が向上しますが、 $2\sim3\Omega$ 以下は推奨しません。一般に、ゲート抵抗はシステムのEMC性能を下げる可能性のあるゲート・ソース間ループの発振を抑制する効果があります。したがって、ゲート抵抗の値が低い場合はドライバ・ループのループ・インダクタンスをできるだけ小さくすることが重要です(詳細は「PCBレイアウトの影響」を参照)。

AN50005

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

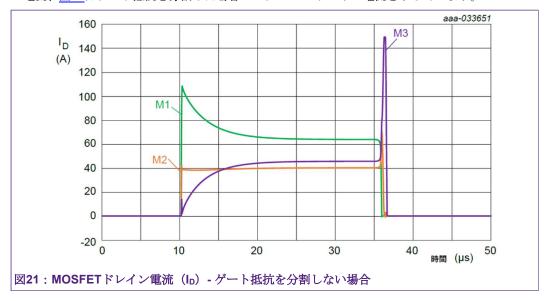

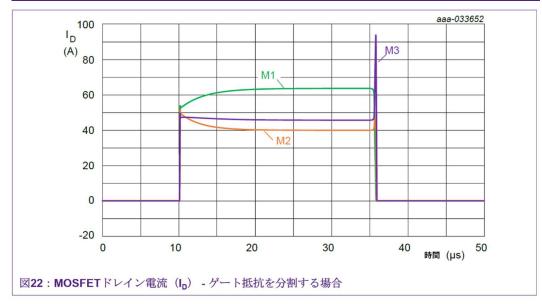

抵抗分割の大きなメリットは、同じハーフブリッジ回路で2種類のゲート抵抗を設定し、ある程度の個体差を設けた上でシミュレーションすることにより、容易に理解することができます。今回はすべての個体差を任意に組み合わせました。図21はゲート抵抗を分割しない場合のMOSFETのドレイン電流、図22はゲート抵抗を分割した場合のMOSFETのドレイン電流を示しています。

シミュレーションの設定と結果を<u>表12</u>と<u>表13</u>、まとめの比較を<u>表14</u>に示します。電源ON時にはM1のQ $_{G(tot)}$ とV $_{GS(th)}$ の両方が低いため、まずM1がスイッチングして大部分の電流を流します。一方、MOSFETの電源をOFFにした時は、入力電荷の小さいデバイス(M3)のスイッチングが最後になるため、こちらが電流の大部分を受け持ちます。

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

表12: ゲート抵抗を分割しない場合のシェアリングのまとめ  $R_G = 39 \Omega$

| デバイス | RDSon<br>[mΩ] | VGS(th) [V] | QG(tot)<br>[nC] | Esw [µJ] | エネルギ<br>ーシェア<br>リ ン グ<br>(スイッ<br>チング) | Есоно [µJ] | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|---------------|-------------|-----------------|----------|---------------------------------------|------------|-----------------------------|

| M1   | 0.62          | 3.21        | 94.4            | 42.7     | 9.6%                                  | 62.2       | 47.0%                       |

| M2   | 1             | 3           | 125.7           | 29.0     | 6.5%                                  | 35.2       | 26.6%                       |

| M3   | 0.88          | 2.79        | 158.0           | 373.0    | 83.9%                                 | 34.9       | 26.4%                       |

ゲート抵抗を分割した場合、電力損失はM3で3.8W、M2で2.0W、M1で1.6Wです。電源ON時もOFF時もピークがほぼ同じになり、改善されていることは明らかです。後者ではM3のピーク電流が約150Aから約90Aに減少しています。導通時のシェアリングも向上していますが、これは電源ONに電流が導通値に達するまでに時間がかかるためです。M3の損失電力は全体で50%減少しています。

表13: ゲート抵抗を分割する場合のシェアリングのまとめ  $R_{G,drv}$  = 12  $\Omega$  and  $R_{G,split}$  = 3.9  $\Omega$

| 20.00 | 1 15m1/2 C 75 H      | 4 / W M I   | / / / /      | 12 04 C 12 11 | 5,aiv == e. |       | 0.0   |

|-------|----------------------|-------------|--------------|---------------|-------------|-------|-------|

| デバイス  | R <sub>DSon</sub> [m | VGS(th) [V] | QG(tot) [nC] | Esw [µJ]      | エネルギ        | ECOND | エネルギー |

|       | Ω]                   |             |              |               | ーシェア        | [µJ]  | シェアリン |

|       |                      |             |              |               | リング         |       | グ     |

|       |                      |             |              |               | (スイッ        |       | (導通)  |

|       |                      |             |              |               | チング)        |       |       |

| M1    | 0.62                 | 3.21        | 94.4         | 30.0          | 12.4%       | 52.3  | 39.6% |

| M2    | 1                    | 3           | 125.7        | 60.6          | 25.1%       | 38.2  | 28.9% |

| М3    | 0.88                 | 2.79        | 158.0        | 150.5         | 62.4%       | 41.4  | 31.5% |

|       |                      |             |              |               |             |       |       |

表14:ゲート抵抗を分割する場合としない場合の比較のまとめ

| デバイス | 全エネルギーシェアリング  |              |  |

|------|---------------|--------------|--|

|      | ゲート抵抗を分割しない場合 | ゲート抵抗を分割する場合 |  |

| M1   | 18.1%         | 22.1%        |  |

| M2   | 11.12%        | 26.5%        |  |

| M3   | 70.7%         | 51.4%        |  |

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 6.2. ソース経路の素子

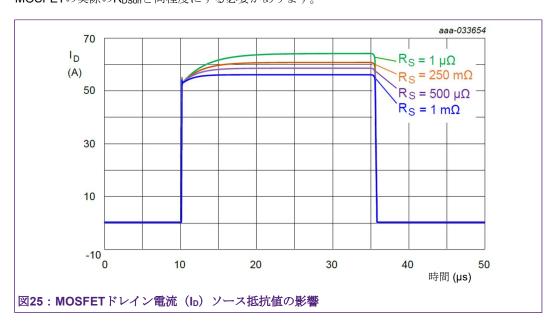

MOSFETの各ソース経路に直列で抵抗を挿入することで、導通時のシェアリングを向上させることができます。一番の欠点としては電力損失源が増えるため、システム全体の効率が下がり、冷却システムの負担が増えることが挙げられます。比較的高い抵抗が必要であることから、この方法はあらゆる状況で通用するわけではありません。

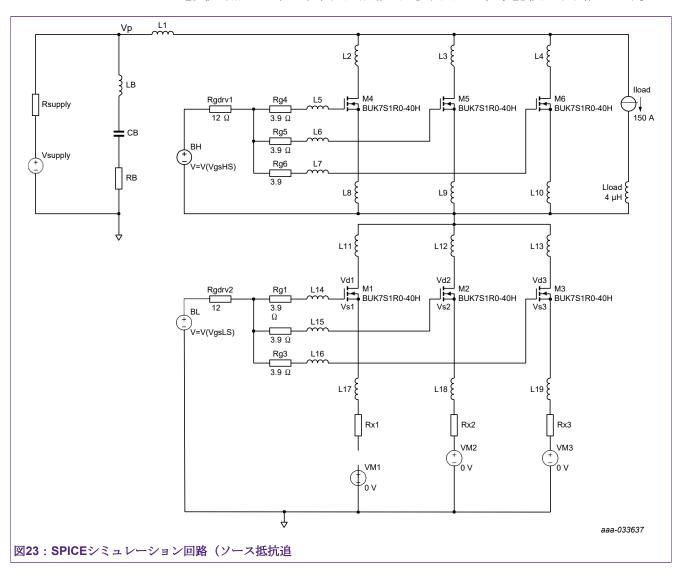

ハーフブリッジに流れる電流をモニターするための直列抵抗がすでに含まれている設計もあります。しかし、並列接続されたMOSFETの場合、抵抗を図23のようにゲート・ソースのループ内に配置する場合のみ有効です。電流検出をする場合、各ループをデカップリングする小さな抵抗を追加して各分岐回路間の潜在的なクロストークを低減することも可能です。

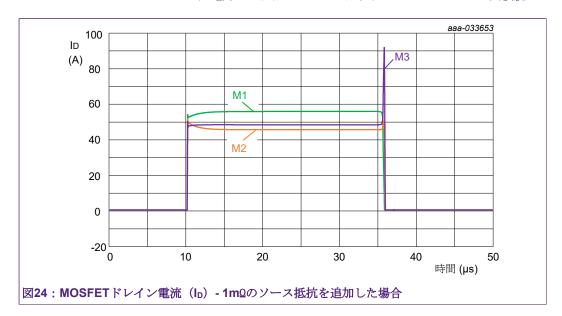

この抵抗はR<sub>DSon</sub>の個体差を解消し、導通時の電流シェアリングを向上させる効果もあります。同じ場所にインダクタンスを配置すると、スイッチング時の電流の急激な変化(dl/dt)に対抗し、ピーク電流を抑えることで類似の電流シェアリング改善効果があります。一方、電流がFET1つあたりの電流値(*ltot / nFET*)に収束する時定数が大きくなるため、導通損失はやや増加します。

表15はシミュレーションの設定と結果をまとめたものです。

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

表15:1m2のソース抵抗を追加した場合のシェアリングのまとめ

| デバイス | RDSon<br>[mΩ] | VGS(th) [V] | QG(tot)<br>[nC] | Esw [µJ] | エネルギ<br>ーシェア<br>リ ン グ<br>(スイッ<br>チング) | Есоид [µЈ | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|---------------|-------------|-----------------|----------|---------------------------------------|-----------|-----------------------------|

| M1   | 0.62          | 3.21        | 94.4            | 27.9     | 11.5%                                 | 41.6      | 30.8%                       |

| M2   | 1             | 3           | 125.7           | 66.5     | 27.4%                                 | 47.3      | 35.1%                       |

| М3   | 0.88          | 2.79        | 158.0           | 148.4    | 61.1%                                 | 46.1      | 34.1%                       |

電流シェアリングに対する抵抗の有効性は、その値によって異なります。電流シェアリングのバランスをとることが目的なら、抵抗は高い方が良いことがわかります(図25)。当然ながらそれに伴って損失も著しく増加します。 $R_{DSon}$ の個体差の影響を効果的に解消するには抵抗をMOSFETの実際の $R_{DSon}$ と同程度にする必要があります。

大電力アプリケーションにおけるパワーMOSFETの並列接続

### 7. PCBレイアウトの影響

並列接続されたMOSFETを用いたアプリケーションの設計では個体差の低減と優れたレイアウトの2つが重要な要素となります。本章で優れたレイアウトを設計するためのガイドラインと、寄生が電流シェアリングに与える影響について説明します。

MOSFETの並列接続において、各種の特性が最も低いデバイスと最も高いデバイスがどこに配置されるかを事前に把握することは不可能です。したがって、各分岐回路を同じレイアウトにすることが重要です。同じレイアウトにしなければ、最悪と想定される状況がさらに悪化することになります。

### 7.1. レイアウト依存の寄生素子

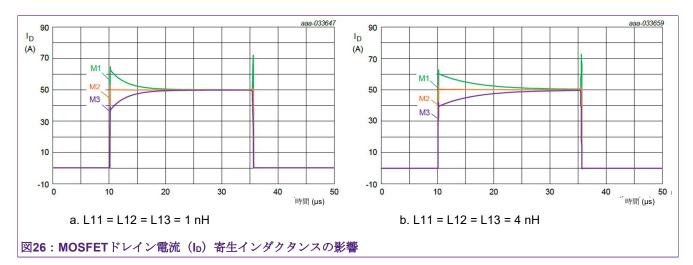

並列接続されたデバイスの場合、経路のループ・インダクタンスと抵抗を最小化するだけでなく各分岐回路で等しくする必要があります。

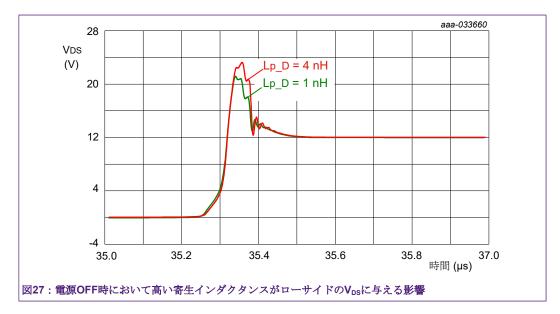

インダクタンスが大きくなると、回路の時定数( $\tau = L/R$ )も大きくなり、電流が定常値に達するのが遅くなります(図26参照)。インダクタンスによってピーク

電流がやや下がりますが、全体的なシェアリングの不均衡は増加します。また、回路におけるキャパシタンスの共振により、Vos(およびVos)の電圧オーバーシュートと発振がハイサイドとローサイドの両方で発生します。また、隣接する回路や配線への干渉も大きくなります。

一般に、単一の(並列接続でない)MOSFETに対して推奨されるルールなら、この場合にも適用できます。ハーフブリッジのスイッチング動作の詳細とEMCに関する考慮事項については、

『AN90011: Half-bridge MOSFET switching and its impact on EMC(ハーフブリッジMOSFETスイッチングとそれがEMCに与える影響)』<sup>22</sup>をご覧ください。

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

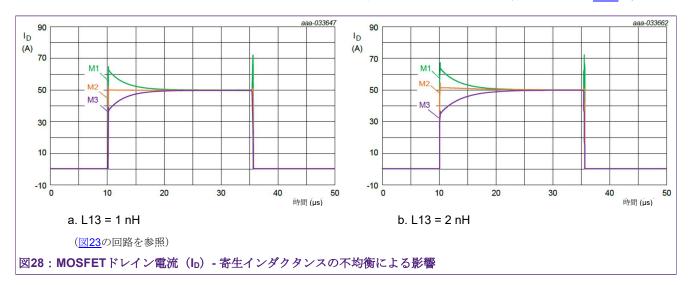

ループ・インダクタンス間に差があると、電流シェアリングに悪影響を与えます(図28)。

### 7.2. 回路レイアウト

他の多くの状況と同様、レイアウトは電子システムの最終的な性能に大きく影響します。部品の品質と同じくらい重要だといえます。並列接続されたMOSFETの場合、デバイス間の熱的なつながりを向上させ、ゲート・ソースのループ、ソース・ドレインのループのインダクタンスと、分岐回路間の抵抗を低く均等にするようなレイアウト設計にする必要があります。

熱結合が良好なら、デバイスは同じ程度の低い温度で動作できます。さらに、各MOSFETのマウンティングベース・周囲間熱抵抗Rth(mb-amb)がほぼ同じになるような設計が望まれます。多層基板やサーマル・ビアを導入すると、デバイスと環境との熱移動特性が向上します。MOSFETの配置には注意が必要です。たとえば、MOSFETの一部をヒートシンクやコネクタなどの近くに配置すると、他の並列接続されたMOSFETよりも温度が低くなる可能性があります。このトピックの詳細については『AN90003: LFPAK MOSFET thermal design guide(LFPAK MOSFET熱設計ガイド)』[3]をご覧ください。

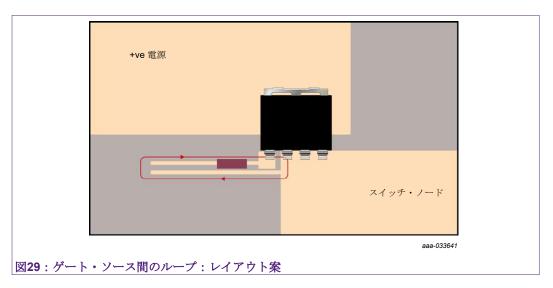

ループ内を低インダクタンスにするにはループの面積を小さくする(自己インダクタンスを小さくする)か、トレースとそのリターンパスをできるだけ近づける(相互インダクタンスを大きくする)とよいでしょう。ゲート・ソース間のループ・インダクタンスを低くするにはドライバをMOSFETにできるだけ近づけ、ゲートとソースを平行に配線します(図29)。

AN50005

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

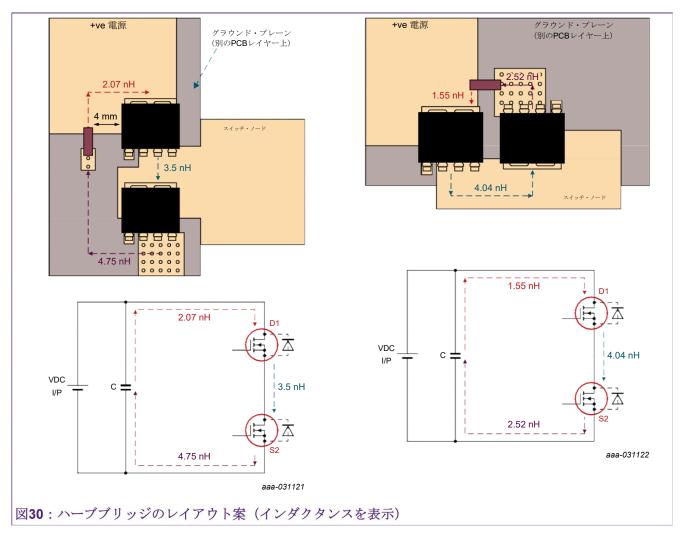

負荷電流が流れるループのインダクタンスは図30のような設計にすると最小限に抑制できます。 詳細は『AN90011: Half-bridge MOSFET switching and its impact on EMC (ハーフブリッジ MOSFETスイッチングとそれがEMCに与える影響) 』 [2]をご覧ください。

インレットとアウトレットの配置は各分岐回路の寄生素子を決定づけるために、重要な役割を担っています。複数デバイスを並列に接続する場合、複数のインレットとアウトレットを使用すると便利な場合があります。小さなケーブルを複数本使用すると、他の面でもメリットがあります。こうした挿入ポイントの場所は注意深く選びましょう。その判断を助ける1つの方法が

AN50005

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

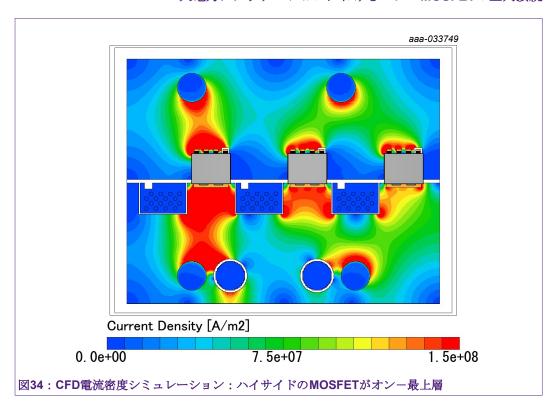

**CFD**ソフトウェアを使った電流密度のシミュレーションです。このようなシミュレーションを実行することで、定常状態 (**DC**) における望ましい電流経路が明確になります。

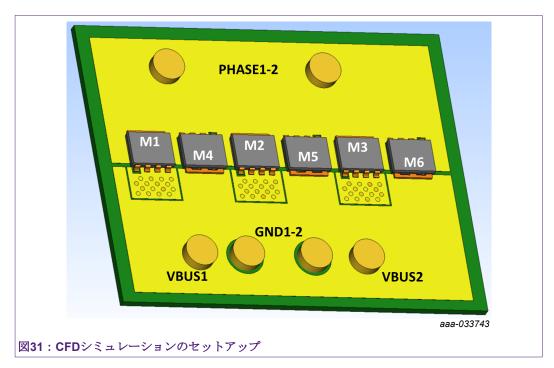

図31にハイサイドとローサイドの両方に3つのMOSFETを配置したシミュレーションのセットアップを示します。ローサイドに配置したMOSFET M1-M3 は基板上層のPHASE1-2と表示されたスイッチング・ノード(インレット)と(図示されていない)下層のグラウンド(アウトレット)の間を多数のフィルド・ビアを介して接続されています。各ハイサイドのMOSFET M4-M6 はスイッチング・ノード(アウトレット)と基板最上層の正電源(インレット)の間に接続されています。並列接続されたデバイスに合計150Aの電流が流れるように設定しています。2つのシミュレーションが必要で、どちらか片側のみがアクティブになるようにします。

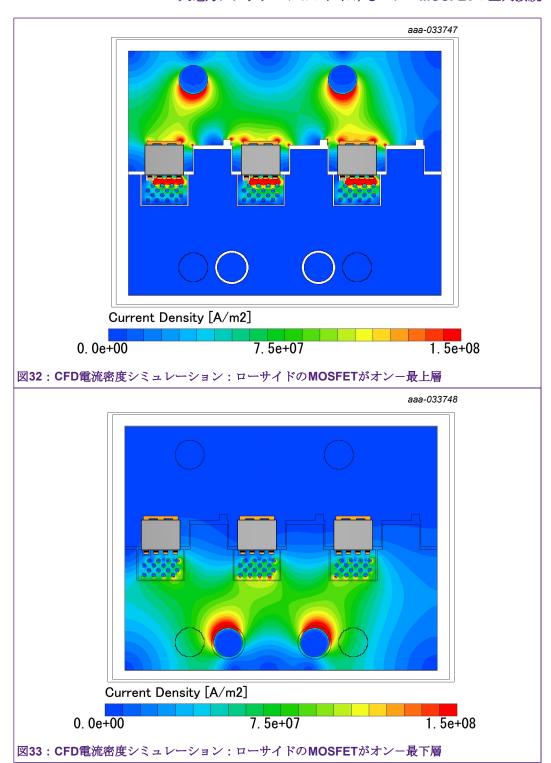

ローサイドとハイサイドの電流密度シミュレーションの結果を図32、図33、図34に示します。赤い部分は電流密度が高い箇所、青い部分は低い箇所です。たとえば、ハイサイドのシミュレーション(図34)ではM4とインレットVBUS1の周辺が赤く、後者の位置関係から電流密度が高くなっています。ダイの表面全体で電流密度を積分すると、レイアウトの定常状態におけるシェアを計算することができます(この例では30~40%)。上記のシミュレーション結果はscSTREAMによって得られました。

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 8. 並列接続されたMOSFETの駆動

並列接続されたMOSFETの駆動にはゲート・ドライバを1つのみ使用するのがおすすめです。主な目的はデバイスの動作をできるだけ同期させることです。

ゲート・ドライバには並列接続されたMOSFETの総入力容量を十分に充放電できるピーク電流能力を持たせることが必要です。この要件はMOSFETの数が増えるほど難しくなります。特に、スイッチング時間を短くする必要がある場合には総入力容量が $C_{iss,tot} = n.FETs \times C_{iss,max}$ となるため、注意してください。これを怠ると、スイッチング速度がゲート抵抗ではなく、ゲート・ドライバ自身に依存することになります。

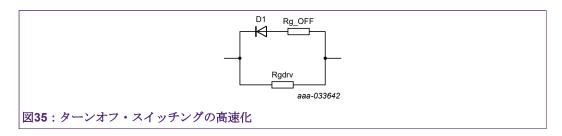

シミュレーションで示したように、ターンオフの方がターンオンより多くのエネルギーを消費します。スイッチング損失を低減する簡単な方法として、ターンオフ時のみ $R_{G,drv}$ の抵抗値を小さくするという方法があります。 $R_{G,drv}$ と並列に低抵抗とダイオードの直列の組み合わせを使用することで、これが実現できます(図35)。しかし、 $R_{G,OFF}$ の適切な値を選ぶ前に回路内に存在する可能性のある寄生インダクタンスを考慮することをおすすめします。高速ターンオフと高インダクタンスの組み合わせはアバランシェを引き起こす可能性があり、並列構成の場合、降伏電圧の低いデバイスに大きなストレスを与える可能性があるからです。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 9. シミュレーション・ツール

本章では複数のMOSFETを並列接続した環境でワースト・ケース・シナリオを見つけることを 目的としたシミュレーションのセットアップ方法を説明します。今回はSPICEを使用しましたが、 同じ機能を持つシミュレーション・ツールなら同じ考え方が適用できます。

すなわち、通常の部品における公差と同じようにシミュレーション内でMOSFETの個体差を考慮しようというものです。ここでは確率分布シミュレーションとワースト・ケース・シナリオを想定したシミュレーションの2種類を議論します。

確率分布シミュレーションとは1つまたは複数のパラメータをその確率分布によって定義するシミュレーションを指し、一般にほぼガウス分布(正規分布)になることが示されています。このようなシミュレーションには、起こりうる組み合わせに確率で重み付けができるというメリットがあります。理論的にはその方が現実に近い評価が得られ、設計のBOM(部品表)に合わせて何度もシミュレーションを実行できます。しかし、実際にはこのような評価はあまり役に立ちません。なぜなら、パラメータ分布に相当するデータ(主にシグマ値)を個々の部品名に対して測定する必要があり、保証された値ではないうえに、製造工程でコストの高い工程を追加しなければならないからです。

分布をベースとするシミュレーションでワースト・ケース・シナリオを設定すれば、パラメータ 代表値の最大分布のみを考慮することになるため、シミュレーション回数を減らすことができます。シミュレーション回数は $2^N+1$ に減少します。ただし、Nはインデックスされたパラメータの数、1は公称値のケースで最後に計算します。この種の評価はデータシート記載の保証された値をベースとします。一方で「外れ値」、すなわち最大値、最小値、公称値のみを考慮した場合よりも結果が悪い分散内にある値を見逃す可能性もあります。

分析には以下の4つのデータが必要です。

- 分散(代表値と∆(公差))

- さまざまな組み合わせのインデックスを生成するbinary(run, index)関数

- インデックスを読み取り、正しいパラメータ値を出力するwc(nominal, tol, index)関数

- 1サイクルの平均電力損失を自動測定する関数

また、分散は対称でなくてはならないため、Rosonの評価はデータシート上の値よりも高い最小抵抗または最大抵抗を使用することになります。QG(tot)などの最小値がデータシートに記載されていない場合はその中間点を公称値として考えることができます。

シミュレーションを実行する前に、各MOSFETのSPICEモデルを修正し、評価で考慮する各パラメータの値をwc(nom, tol, index) 関数の出力で置き換える必要があります(下図)。

- R<sub>DSon</sub>の代表値は0.88m Ω、公差は±0.12m Ω

RD 3 4 {wc(576.2603u,tol\_RD,3)} TC= 9.735m, 2.369u

- Q<sub>GS</sub>の代表値は33.5 nC、公差は± 13 nC CGS 2 6 {wc(7.67n,tol\_CGS,6)}

- QGDの代表値は25.5 nC、公差は± 17 nC

.params CGD\_scale = {wc(1.245,tol\_CGD,9)}

...G11 3 2 VALUE {CGD\_scale\*V(13,0)\*I(V11)}

- V<sub>GS(th)</sub>の代表値は3 V、公差は±0.21 V

Vto= {wc(3.843,tol\_VGSth,0)}

ただし、tol\_RD = 119.68u, tolCGS = 1.57n, tol\_CGD = 0.405 and tol\_VGSth = 0.21

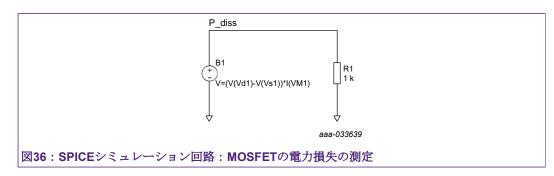

この場合、パラメータは4つで、並列接続された3つのMOSFET間で変動するため、インデックス化されたパラメータの総数は12となります。そのため、組み合わせ総数は $2^{12}+1=4097$ となります。この評価では1つのMOSFETのみを考慮します。このシミュレーションには図1の回路を小変更したものを使用します。また、調査対象のMOSFETの電力損失を自動的に算定するために、図36に示す小回路(と対応するモニター用0V電圧源)が必要です。

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

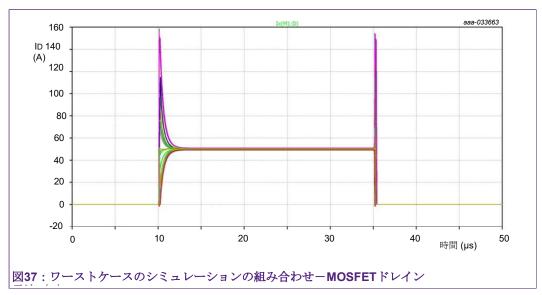

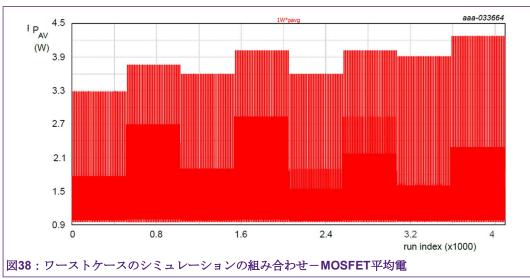

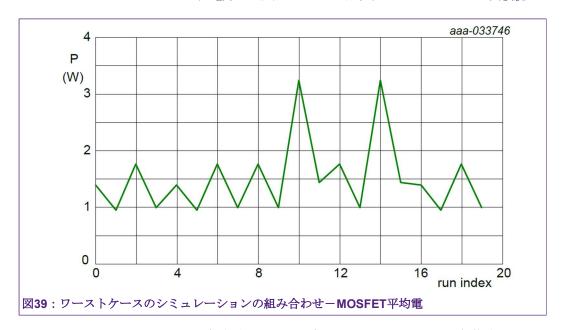

シミュレーションが完了すると、M1に流れる電流を表示させることができます。最終結果を図37、図38、図39に示します(図39はシミュレーション結果を20回目まで表示)。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

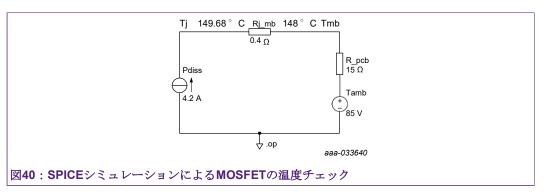

ワーストケースは1つのMOSFETの損失電力が4.2Wに達したときでした。 $V_{GS(th)}$ の個体差のみを考慮した場合のワーストケースでは1つのMOSFETの電力損失が1.7W程度でした。この結果は図40に示すように、ジャンクション部の定常(DC)的な熱特性をモデル化した簡単な回路で得ることができます。この場合、ジャンクション部温度を最大でも175 $^{\circ}$ C以下に保つために、15K/W程度の熱抵抗を持つ基板が必要となります。これにより、MOSFETとPCB間の界面温度がFR4の定格より高くなるため、IMSやDBC基板が必要になる場合もあります。代替として、MOSFETを1つ追加したり、さらにRDSonが低いMOSFETを選択することも考えられます。

この考え方は、多くのシナリオに適用可能です。たとえば、さまざまなデューティ・サイクルを想定してそれぞれのワーストケースを評価し、その電力値をot 240に示す回路の電流源に挿入することも可能です。さらに、ワーストケースの瞬時電力波形をエクスポートし、ot RCサーマルネットワーク内で使用して、その時のジャンクション温度がot 175 ot C以下であることを確認することもできます。

#### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### 10. まとめ

本アプリケーション・ノートの目的は並列接続されたMOSFET間のシェアリングがRoson、Ves(th)、QG(tot)などのパラメータの個体差やPCBレイアウトによってどのような影響を受けるかを示すことです。分析はスイッチモード(PWM)アプリケーション、すなわちハーフブリッジ回路を考慮して行いました。

スイッチング時の電流の不均衡に最も大きく影響するのが $V_{GS(th)}$ の個体差で、ターンオンとターンオフのときに同じように影響します。 $V_{GS(th)}$ が低いデバイスが最初に電源ONになり、最後に電源OFFになるため、どちらにおいても多くの電力を消費します。また、 $V_{GS(th)}$ はNTC(負の温度係数)を持っており、電流が多く流れるMOSFETの $V_{GS(th)}$ がさらに下がるため、電力損失が増加します。 $Q_{G(tot)}$ の個体差はゲート抵抗をMOSFETのゲートに近い場所とドライバ側の共通抵抗に分割することで、効果的に打ち消すことができます。この変更により、スイッチング時のシェアリングに大きな改善効果があります。

MOSFETが並列接続されていることを考慮すると、 $R_{DSon}$ の影響は $V_{GS(th)}$ ほど顕著ではありません。 PTC(正の温度係数)を持つため、導通時にシェアリングが向上し、 $R_{DSon}$ の個体差に伴う不均衡を打ち消すからです。また、導通時の損失( $I^2 \times R$ )は、通常、スイッチング損失よりも小さいため、不均衡が全体の電力シェアリングに与える影響は小さくなります。

並列接続したデバイスの性能の定量評価に、ワーストケースを想定したシミュレーションを使用することができます。どのデバイスを何個並列接続するかを把握するのに有効です。ワーストケースは主に特定のパラメータの分散に依存します。 $V_{GS(th)}$ のロット分散はデータシート記載の値の半分程度であることが示されました。保証値ではないものの、ロット分散を使った方がより現実的であり、高い性能をもたらす設計をすることができます。

大電力アプリケーションにおけるパワーMOSFETの並列接続

## 11. 付録

## 11.1. 実測結果

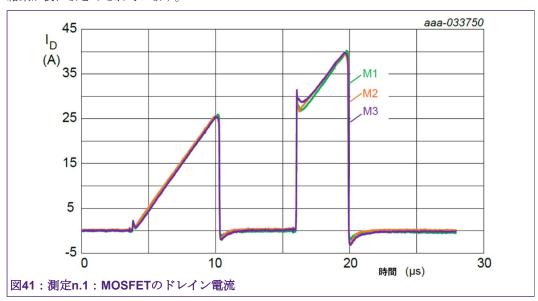

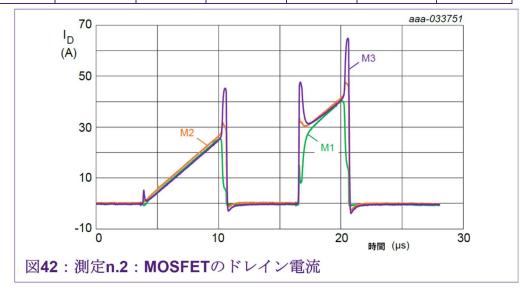

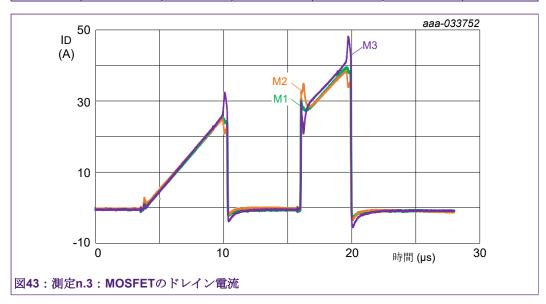

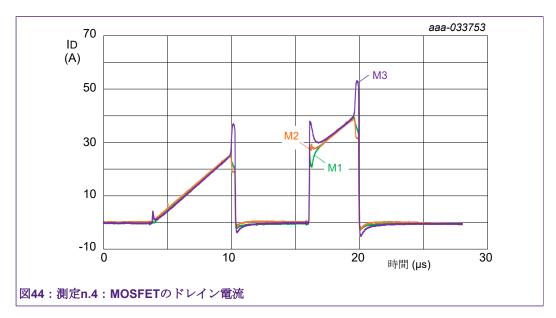

下のデータはローサイドの並列接続された3つのMOSFETに流れる電流の最初の2パルスを示したものです。回路トポロジーは $4\mu$  Hの誘導性負荷を駆動するハーフブリッジを使用しています。4種類の測定を示します。M1、M2、M3の $R_{DSon}$ 、 $Q_{G(tot)}$ 、 $V_{GS(th)}$ (1mAと1Aの両方で測定)の測定結果が表にまとめられています。

表16: 測定n.1のまとめ

| A TO . WINCH | .1020                      |              |                                  |                     |                                         |                             |

|--------------|----------------------------|--------------|----------------------------------|---------------------|-----------------------------------------|-----------------------------|

| デバイス         | R <sub>DSon</sub> [m<br>Ω] | QG(tot) [nC] | V <sub>GS(th)</sub> [V]<br>@1 mA | VGS(th)<br>[V]@ 1 A | エネルギ<br>ーシェ ア<br>リ ン イッ<br>(スイッ<br>チング) | エネルギー<br>シェアリン<br>グ<br>(導通) |

| M1           | 3.16                       | 35.57        | 3.02                             | 3.62                | 33.7%                                   | 33.1%                       |

| M2           | 3.02                       | 36.45        | 3.02                             | 3.63                | 32.5%                                   | 32.9%                       |

| М3           | 2.94                       | 35.64        | 3.02                             | 3.62                | 33.8%                                   | 34.0%                       |

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

表17: 測定n.2のまとめ

| デバイス | R <sub>DSon</sub> [m<br>Ω] | QG(tot) [nC] | V <sub>GS(th)</sub> [V]<br>@1 mA | V <sub>GS(th)</sub><br>[V]@ 1 A | エネルギ<br>ーシェア<br>リ ン グ<br>(スイッ<br>チング) | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|----------------------------|--------------|----------------------------------|---------------------------------|---------------------------------------|-----------------------------|

| M1   | 3.07                       | 38.14        | 3.46                             | 4.10                            | 8.2%                                  | 32.8%                       |

| M2   | 2.94                       | 35.64        | 3.02                             | 3.62                            | 36.1%                                 | 33.7%                       |

| М3   | 3.14                       | 33.74        | 2.80                             | 3.39                            | 55.7%                                 | 33.5%                       |

表18: 測定n.3のまとめ

| デバイス | R <sub>DSon</sub> [m<br>Ω] | QG(tot) [nC] | V <sub>GS(th)</sub> [V]<br>@1 mA | VGS(th)<br>[V]@ 1 A | エネルギ<br>ーシェ ア<br>リ ン イッ<br>( スイッ<br>チング) | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|----------------------------|--------------|----------------------------------|---------------------|------------------------------------------|-----------------------------|

| M1   | 3.16                       | 35.57        | 3.02                             | 3.62                | 32.0%                                    | 32.9%                       |

| M2   | 3.43                       | 28.69        | 3.03                             | 3.63                | 32.0%                                    | 32.9%                       |

| М3   | 3.05                       | 44.50        | 3.02                             | 3.62                | 36.0%                                    | 34.2%                       |

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

表19: 測定n.4のまとめ

| デバイス | R <sub>DSon</sub> [m<br>Ω] | QG(tot) [nC] | V <sub>GS(th)</sub> [V]<br>@1 mA | VGS(th)<br>[V]@ 1 A | エネルギ<br>ーシェア<br>リ ン グ<br>(スイッ<br>チング) | エネルギー<br>シェアリン<br>グ<br>(導通) |

|------|----------------------------|--------------|----------------------------------|---------------------|---------------------------------------|-----------------------------|

| M1   | 3.16                       | 35.57        | 3.02                             | 3.62                | 25.5%                                 | 33.2%                       |

| M2   | 3.05                       | 44.50        | 3.02                             | 3.62                | 27.5%                                 | 33.2%                       |

| М3   | 3.14                       | 33.74        | 2.80                             | 3.39                | 45.3%                                 | 33.6%                       |

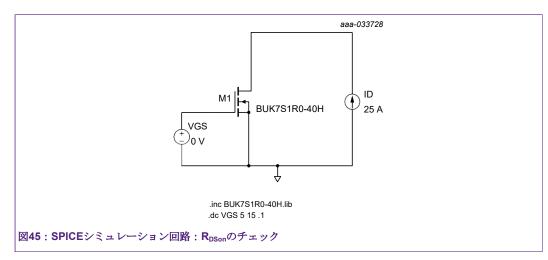

### 11.2. シミュレーション

以下のシミュレーションはSPICEモデルがデータシートに適合していることを検証するために使用できます。

### RDSonのシミュレーション

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### QG(tot)のシミュレーション

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

### VGS(th) (V)

大電力アプリケーションにおけるパワーMOSFETの並列接続

# 12. 参考文献

- 1. 『The Art of Electronics(電子工学の作法)』、Paul Horowitz and Winfield Hill: § 3.6.3. 「Paralleling MOSFETs(MOSFETの並列接続)」、ページ213

- **2** AN90011: Half-bridge MOSFET switching and its impact on EMC(ハーフブリッジMOSFETスイッチングとそれがEMCに与える影響)

- 3. AN90003: LFPAK MOSFET thermal design guide(LFPAK MOSFET熱設計ガイド)』

- 4. BUK7S1R0-40H データシート

# 13. 改訂履歴

### 表20:改訂履歷

| 改訂番号 | 日付          | 内容                                 |

|------|-------------|------------------------------------|

| 1.1  | 2021年09月13日 | 微修正、 <u>表12</u> と <u>表14</u> の値を修正 |

| 1.0  | 2021年09月07日 | 第1版                                |

大電力アプリケーションにおけるパワーMOSFETの並列接続

### 14. 法的な記載事項

#### 定義

ドラフトー本書はドラフト版のみです本書の内容は社内レビュー中であり、正式な承認が得られていません。今後、修正/加筆される可能性があります。 Nexperiaは本書に含まれる情報の正確性または完全性に関して、いかなる表明、保証をせず、情報を使用した結果に対していかなる責任も負わないものとします。

#### 免責事項

限定保証と責任 - 本書に記載されている内容は、正確で信頼できるものであると考えられます。しかしながら、Nexperiaは情報の正確性または完全性について、明示または黙示を問わず、いかなる表明または保証を行うものではなく、

また、これらの情報を使用した結果に対して、いかなる責任も負わないものとします。Nexperiaは本書の内容のうち、当社以外の情報源から得られたものについては一切の責任を負いません。

Nexperiaは間接的、付随的、懲罰的、特別な損害または結果的損害 (利益の損失、貯蓄の損失、事業の中断、製品の除去または交換に関 する費用、手直し費用など) について、その損害が不法行為(過失を 含む)、保証、契約違反またはその他の法的理論に基づいているかど うかにかかわらず、いかなる場合も責任を負わないものとします。

理由のいかんを問わず、またお客様が被る可能性のある損害にかかわらず、 Nexperiaが本書記載の製品についてお客様に対して有する責任の総和および 累積はNexperiaの商業販売条件に従って制限されるものとします。

変更権 - Nexperiaは本書に掲載された情報(仕様および製品説明を含むがこれに限定されない)をいつでも予告なく変更する権利を有するものとします。本書の内容は以前に発表されたすべての情報を更新し、置き換えるものです。

使用時の適合性 - Nexperia 製品は故障や誤作動が人身事故、死亡事故、深刻な財産の損害/環境破壊につながることが合理的に予想される場合において、

生命維持装置/システム、生命維持に不可欠な装置/システム、安全性が極めて重要な装置/システムとしての使用に適した設計、認可、保証がされていません。NexperiaおよびそのサプライヤはNexperia製品を上記の機器や用途に組み込んだり、使用したりすることに関して一切の責任を負いません。そのような行為にあたってはお客様の責任において行ってください。

アプリケーション - 本書で記載されている製品のアプリケーションは例示を目的としたものに過ぎません。Nexperiaは本書で記載するアプリケーションがさらなるテストや修正を行わずに特定の用途に適合することを表明または保証するものではありません。

Nexperia製品を使用してアプリケーションや製品の設計/運用を行うことはお客様の責任であり、Nexperiaはアプリケーションやお客様の製品設計に関するいかなるサポートも提供しません。Nexperia製品がお客様のアプリケーションや製品、

またお客様のサードパーティー顧客の用途や使用に適しているかどうかは、お客様の責任において判断してください。

お客様はアプリケーションや製品に関連するリスクを最小化するために、 適切な設計および運用のセーフガードを提供する必要があります。

Nexperiaはお客様のアプリケーションや製品、またはお客様のサードパーティー顧客のアプリケーションや使用に起因する不具合、損害、費用、問題に対して一切の責任を負わないものとします。お客様はNexperia製品を使用するアプリケーションおよび製品、またはお客様のサードパーティー顧客によるアプリケーションまたは使用の不履行を回避するために、必要なすべてのテストを行う責任を負うものとします。Nexperiaはこの点に関して、いかなる責任も負わないものとします。

**輸出管理** - この文書およびここに記載されている品目は輸出管理規制の 対象となる場合があります。輸出する場合は所轄官庁の事前承認が必要 な場合があります。

**翻訳**-英語以外の(翻訳された)ドキュメントはあくまで参考用途としてご使用ください。翻訳版と英語版の間に矛盾がある場合、英語版が優先されるものとします。

#### 商標

注:本書で参照されるすべてのブランド、製品名、サービス名および商標はそれぞれの所有者の所有物です。

AN50005

本書に記載されている内容は法的な免責事項の対象となります。

© Nexperia B.V. 2021 All rights reserved

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

# 表一覧

| 表1:MOSFETの個体差がない理想的なケースのまとめ6                                                    |

|---------------------------------------------------------------------------------|

| 表2: データシート上のBUK7S1R0-40Hの特性 RDSon7                                              |

| 表3:RDSonの個体差を求めるカスタム版SPICEモデル7                                                  |

| 表4:RDSonの個体差による影響のまとめ8                                                          |

| 表5:データシート上のBUK7S1R0-40Hの特性:<br>ゲート電荷8                                           |

| 表6:QG(tot)の個体差を求めるカスタム版SPICEモデル9                                                |

| 表7:QG(tot)の個体差による影響のまとめ10                                                       |

| 表8:データシート上のBUK7S1R0-40Hの特性: VGS(th)10                                           |

| 表9:VGS(th)の個体差を求めるカスタム版SPICEモデル.10                                              |

| 表10:VGS(th)の個体差による影響のまとめ11                                                      |

| 表11:VGS(th)のロット分散の影響のまとめ17                                                      |

| 表12:ゲート抵抗を分割しない場合のシェアリングのまとめ<br>: RG = 39 Ω19                                   |

| 表13:ゲート抵抗を分割する場合のシェアリングのまとめ:RG,drv = 12 $\Omega$ and RG,split = 3.9 $\Omega$ 19 |

| 表14:ゲート抵抗を分割する場合としない場合の比較のま<br>とめ19                                             |

| 表15:1mΩのソース抵抗をした場合のシェアリング<br>のまとめ                                               |

| 表16:測定n.1のまとめ32                                                                 |

| 表17: 測定n.2のまとめ33                                                                |

| 表18: 測定n.3のまとめ33                                                                |

| 表19: 測定n.4のまとめ34                                                                |

| 表20:改訂履歴                                                                        |

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

図27:電源OFF時において高い寄生インダクタンスが

|                                                             | ローサイトのVDSに与える影響23                             |

|-------------------------------------------------------------|-----------------------------------------------|

| 図1:SPICEシミュレーション回路(ハーフブリッジ)3                                | 図28: MOSFETドレイン電流 (ID) 寄生インダクタンスの不均衡による影響23   |

| 図2:MOSFETのドレイン電流(ID)とエネルギー損                                 | 図29:ゲート・ソース間のループ:レイアウト案24                     |

| 失(Ediss)-MOSFETの個体差がない理想的なケース。<br>ターンオン、導通、ターンオフのフェーズ       | 図30: ハーブブリッジのレイアウト案(インダクタンスを<br>記載)24         |

| 図3:MOSFETのドレイン電流(ID)とエネルギー損失                                | 図31: CFDシミュレーションのセットアップ25                     |

| (Ediss) と電力損失 (Pdiss) -MOSFETの個体差がない                        |                                               |

| 理想的なケース。ターンオン・フェーズ5                                         | 図32: CFD電流密度シミュレーション: ローサイドの MOSFETがオンー最上層 26 |

| 図4: MOSFETのドレイン電流(ID)とエネルギー損失                               | 図33: CFD電流密度シミュレーション: ローサイドの                  |

| (Ediss) と電力損失(Pdiss) -MOSFETの個体差がない<br>理想的なケース。ターンオフのフェーズ   | MOSFETがオンー最下層 26                              |

|                                                             | 図34: CFD電流密度シミュレーション: ハイサイドの                  |

| 図5: BUK7S1R0-40Hのサブ・スレショルド・ドレイン電<br>流とゲート・ソース電圧の関係7         | MOSFETがオンー最上層27                               |

| 図6: MOSFETドレイン電流 (ID) RDSonの個体差の影響8                         | 図35: ターンオフ・スイッチングの高速化27                       |

| 図7:ゲート電荷波形の定義9                                              | 図36: SPICEシミュレーション回路: MOSFETの電力損失の            |

| 図8: MOSFETドレイン電流(ID)QG(tot)の個体差の影響                          | 測定 29                                         |

| 10                                                          | 図37: ワーストケースのシミュレーションの組み合わせ -                 |

| 図9: MOSFETドレイン電流(ID)VGS(th)個体差の影響                           | MOSFETのドレイン電流 (ID)                            |

| 11                                                          | 図38: ワーストケースのシミュレーションの組み合わせ - MOSFETの平均電力29   |

| 図10: MOSFETにおける電気と熱の関係12                                    | 図39: ワーストケースのシミュレーションの組み合わせ-                  |

| 図11:BUK7S2R5-40Hのデータシートグラフ:伝達特性と<br>ZTC12                   | MOSFETの平均電力30                                 |

| 図12:データシート上のBUK7S2R5-40Hの特性:                                | 図40: SPICEシミュレーションのMOSFET温度チェック               |

| オン抵抗とジャンクション温度の関係(正規化済み) 13                                 |                                               |

| 図13:SPICEシミュレーション回路:熱結合13                                   | 図41: 測定n.1: MOSFETのドレイン電流32                   |

| 図14:熱結合がシェアリングに与える影響:                                       | 図42: 測定n.2: MOSFETのドレイン電流32                   |

| RDSon(M1) = 0.62 m $\Omega$ and RDSon(M2) = 1 m $\Omega$ 14 | 図43: 測定n.3: MOSFETのドレイン電流33                   |

| 図15:BUK7S1R0-40Hデータシートのグラフ:ゲー                               | 図44: 測定n.4: MOSFETのドレイン電流34                   |

| ト・ソース・スレショルド電圧とジャンクション温度<br>の関係 <b>15</b>                   | 図45: SPICEシミュレーション回路: RDSonのチェック 34           |

|                                                             | 図46:SPICEシミュレーション回路:RDSonとVGSの関係              |

| 図16:BUK7S1R5-40Hの各ロットにおけるVGS(th)の分散<br>16                   | 35                                            |

| 図17:2つの連続デバイス間のVGS(th)差(絶対値)16                              | 図47: SPICEシミュレーション回路: QG(tot)のチェック35          |

| 図18: MOSFETドレイン電流(ID) - データシートとロット                          | 図48: SPICEシミュレーション回路: VGSの時間的推移 36            |

| のVGS(th)分散比較 17                                             | 図49: SPICEシミュレーション回路: $VG(th)$ のチェック.36       |

| 図19: SPICEシミュレーション回路: ゲート抵抗を分割する場合、しない場合の比較18               | 図50: SPICEシミュレーション回路: $VG(th)$ のチェック.36       |

| 図20:ゲート抵抗を分割する場合としない場合の                                     |                                               |

| ゲート・ソース間電圧18                                                |                                               |

| 図21:MOSFETドレイン電流(ID)ゲート抵抗を分割しな                              |                                               |

| い場合 18                                                      |                                               |

| 図22: MOSFETドレイン電流(ID) - ゲート抵抗を分割する<br>場合 19                 |                                               |

| 図23: SPICEシミュレーション回路(ソース抵抗追加).20                            |                                               |

| 図24: MOSFETドレイン電流(ID)1mQのソース抵抗をし                            |                                               |

| た場合 21                                                      |                                               |

| 図25: MOSFETドレイン電流 (ID) - ソース抵抗値の影響                          |                                               |

| 21                                                          |                                               |

図―階

### 大電力アプリケーションにおけるパワーMOSFETの並列接続

# 目次

| 1. はじめに2                                  |

|-------------------------------------------|

| 2. アプリケーション2                              |

| 3. 主な仕様2                                  |

| 4. MOSFETの損失とパラメータが                       |

| 電流シェアリングに与える影響4                           |

| 5. パラメータの個体差が                             |

| 電流シェアリングのパフォーマンスに与える影響                    |

| 51. 静的な動作 (DC)                            |

| 5.1.1. ドレイン・ソース間のオン抵抗-RDS <sub>on</sub>   |

| 52 動的な動作                                  |

| 5.2.1. 全ゲート電荷-Q <sub>G(tot)</sub>         |

| 5.2.2. ゲート・ソース間のスレショルド電圧 $-V_{GS(th)}$ 10 |

| 53. 並列接続されたMOSFETと温度依存性12                 |

| 5.3.1. 静的な動作時 (DC)<br>の温度依存性              |

| 5.3.2. 動的な動作時の温度依存性                       |

|                                           |

|                                           |

| 6. 回路の最適化                                 |

| 61. ゲート抵抗の分割    17                        |

| 62 ソース経路の素子                               |

| 7. PCBレイアウトの影響                            |

| 7.1. レイアウト依存の寄生素子                         |

| 72 回路レイアウト                                |

| 8. 並列接続されたMOSFETの駆動27                     |

| 9. シミュレーション・ツール                           |

| 10. まとめ31                                 |

| 11. 付録32                                  |

| 11.1. 実測結果32                              |

| 112 シミュレーション34                            |

| 12. 参考文献37                                |

| 13. 改訂履歴37                                |

| 14. 法的な記載事項38                             |

| © Nexperia B.V. 2021 All rights reserved  |

詳しくはhttp://www.nexperia.comをご覧ください。 営業所のアドレスについては、以下までお問い合わせください。salesaddresses@nexperia.com **発行日:2021年9月13日**