#### **Document information**

| Information | Content                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | Low Temperature Soldering, LTS, SnBiX, board mounting, SMT, reflow                                                                                                                                                                                         |

| Abstract    | This application note investigates SMT assembly using Low Temperature Solder (SnBiX) in reflow lines for Nexperia packages. Board mounting, thermal and mechanical behavior are analyzed. All Nexperia packages can be soldered using SnBiX solder pastes. |

Low temperature soldering, application study

## 1. Introduction

New generation Low Temperature Solder (LTS) pastes for Surface Mount Technology (SMT) is proposed for low temperature applications such as computing. LTS pastes are commonly build on near-eutectic SnBi alloying system and therefore show reduced melting temperatures which reduces the reflow temperatures as well as the energy consumption during SMT by up to 40%. This translates into reduced  $CO_2$  emissions and reduced manufacturing cost. Additionally, such effect can improve the yield impact created by high temperature (HT) warpage. HT warpage is widely recognized seen as main driver to reduce the reflow temperature for SMT. New product markets such as ultra-mobile computing and the Internet of Things (IoT) drive the need for smaller and thinner packages and boards which can suffer warpage by reflow temperatures of current solder systems like SAC. By lowering the peak temperature during reflow, warpage is reduced, resulting in higher SMT yields.

To safeguard the usage of Nexperia products on LTS assembly lines an internal investigation was carried out proving LTS readiness of Nexperia's package families. This application note will give details on the analysis and guideline for possible use of LTS solder.

Since Nexperia's package portfolio consists of various lead finish technologies, family representatives of these technologies were selected and mounted on a printed-circuit board (PCB) using standard SAC and new LTS solder.

## 2. LTS application study

To safeguard potential application of Nexperia products in LTS assembly lines, a range of packages were validated compared to standard SAC solder. By that valuable insights of LTS assembly were gained and will be shared.

Six representative packages were subjected to the following test plan:

- 0 hour characterization:

- Ceramic plate test

- Microsection

- Optical inspection

- · X-ray inspection

- Board level Reliability

- Thermal cycling

- Drop testing

- Mechanical testing

- Shear testing

Low temperature soldering, application study

## 3. Set up and Materials

#### 3.1. Package selection

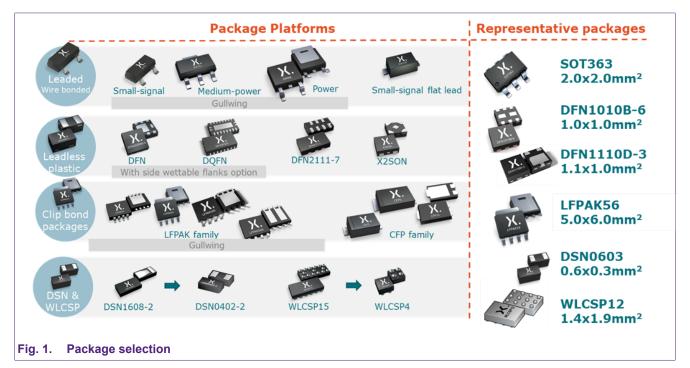

Various packages have been chosen to cover Nexperia's plating and leadframe technologies. Fig. 1 shows the selection. Six products were used in this application study.

This selection covers:

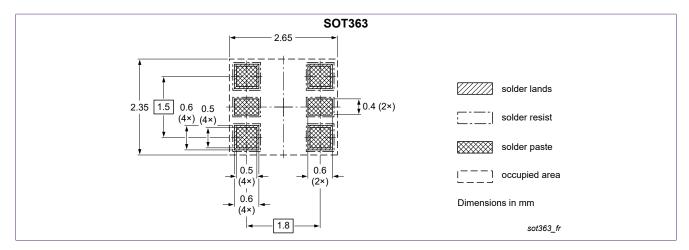

- SOT363: NiFe leadframe + Cu plating and Sn finish

- DFN1010B-6 (SOT1216), DFN1110D-3 (SOT8015) Cu leadframe with NiPdAu plating and Sn finish

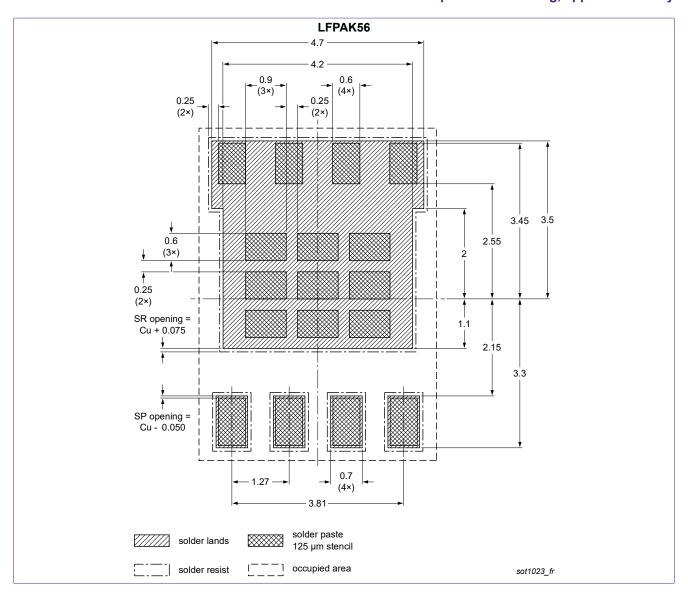

- LFPAK56 (SOT669): Cu leadframe with Sn finish

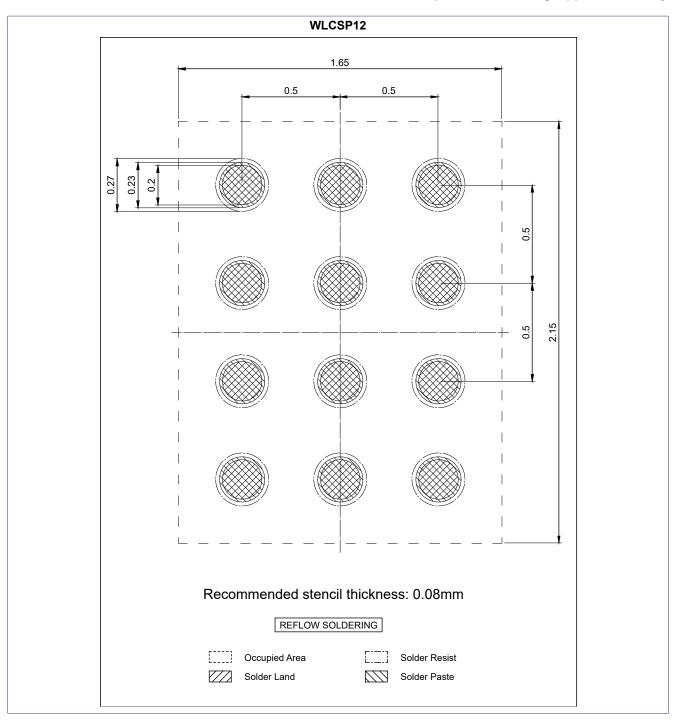

- WLCSP12: WLCSP with SAC solder balls

- DSN0603-2 (SOD962): DSN with CuSn pads

#### 3.2. Footprint and stencil design

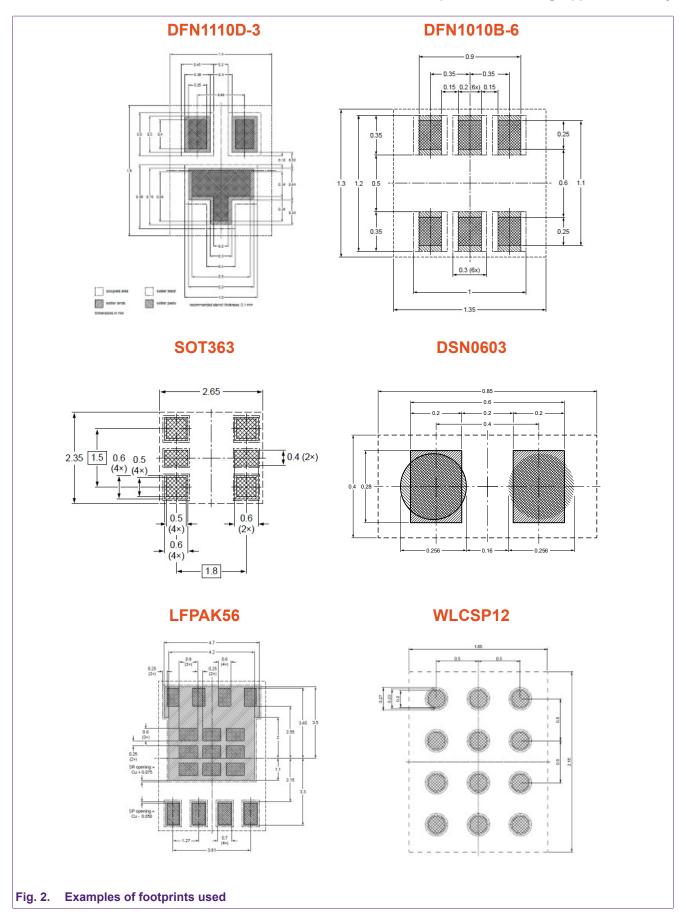

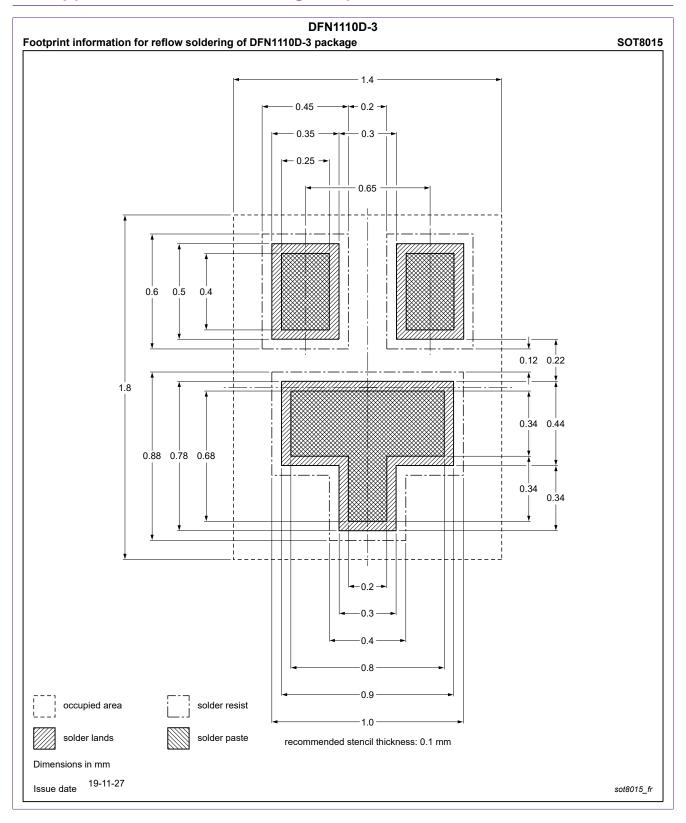

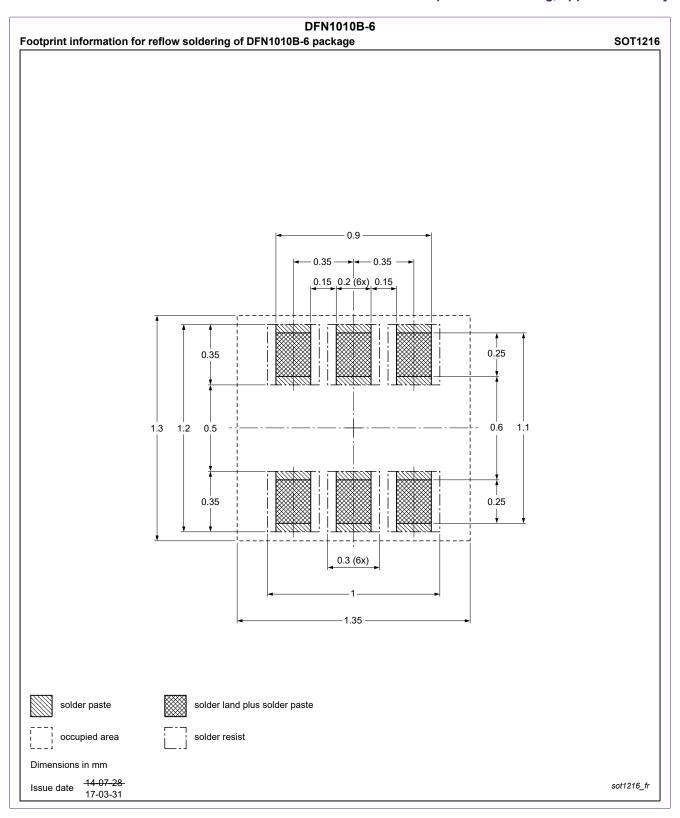

Footprint and stencil design were chosen according to product recommendations for the selected packages, see Fig. 1.

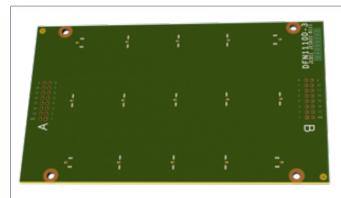

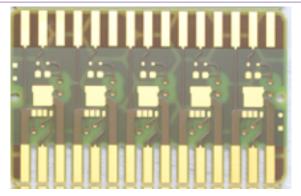

As PCB material, 8 layer FR4 boards according to JESD22-B111/A104 were used. WLCSP12 and DFN1110D-3 were assembled on drop test PCB layout while the other packages were soldered on reliability boards. The footprints used are shown in <u>Fig. 2</u>, (see also <u>Appendix 1</u>) and examples of PCBs in <u>Fig. 3</u>.

### Low temperature soldering, application study

drop test PCB (DFN1110D-3)

reliability test PCB (LFPAK56)

Fig. 3. Examples of drop test PCB and reliability PCB

## 3.3. Solder paste

As Low Temperature Solder paste, a commercially available, near eutectic SnBiX alloy (Sn42Bi57.6Ag0.4) Type 5 was used. As comparison, trails were conducted using SAC305 Type 4.5 alloy. Further paste printing details are shown in <u>Table 1</u>.

Table 1. Solder paste printing details

| Stencil thickness [µm] | Print speed [mm/s]                        | Squeegee force [N]                                                                                                                                      |  |  |  |  |

|------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 80                     | 40                                        | 45                                                                                                                                                      |  |  |  |  |

| 100                    | 35                                        | 49                                                                                                                                                      |  |  |  |  |

| 100                    | 35                                        | 55                                                                                                                                                      |  |  |  |  |

| 100                    | 35                                        | 49                                                                                                                                                      |  |  |  |  |

| 120                    | 35                                        | 49                                                                                                                                                      |  |  |  |  |

| 80                     | 40                                        | 45                                                                                                                                                      |  |  |  |  |

|                        | Stencil thickness [μm] 80 100 100 100 120 | Stencil thickness [µm]       Print speed [mm/s]         80       40         100       35         100       35         100       35         120       35 |  |  |  |  |

#### Low temperature soldering, application study

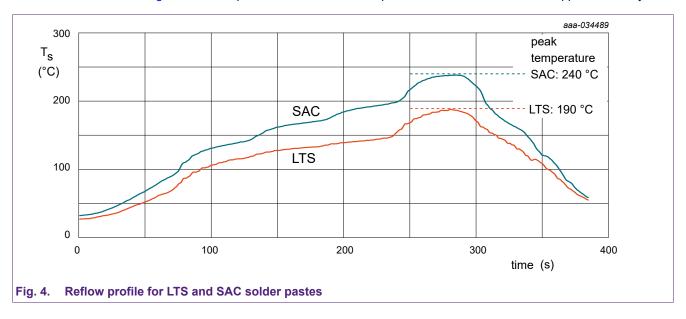

## 4. Reflow profile

Reflow profile should be adjusted according to the data sheet of the solder material supplier. Soldering was done under nitrogen atmosphere.

Fig. 4 shows the profile of SnBiX solder compared to SAC solder used in the application study.

## 5. Results

#### 5.1. 0 hour characterization

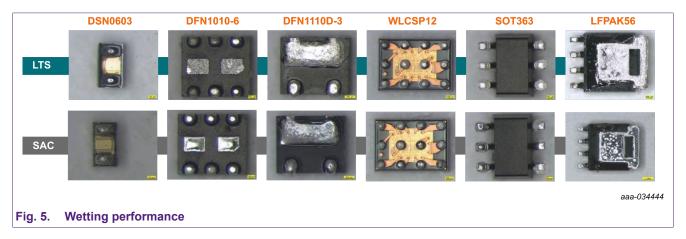

### 5.1.1. Ceramic plate test

In the ceramic plate test, solder paste is printed onto a ceramic substrate, followed by package placement and reflow. Further, the reflowed solder on the leads of the package is visually inspected to determine the wetting characteristics.

- Wetting performance of all packages are according to requirements (>95%)

- No difference in wetting performance between LTS and SAC

#### Low temperature soldering, application study

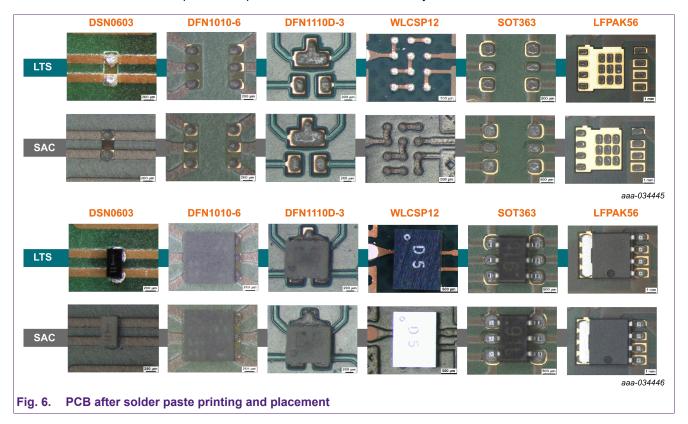

## 5.1.2. Optical inspection

No significant differences between LTS and SAC solder paste except for slightly higher solder paste volume when using LTS solder have been observed. Better release performance of LTS solder paste is suspected because of different flux system.

#### Low temperature soldering, application study

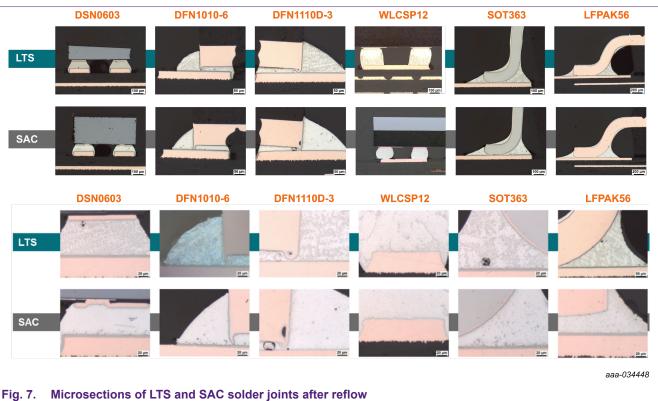

#### 5.1.3. Microsection

Microsection images of all packages confirms good wettability of LTS and SAC solder. Both alloys show homogeneous inter-metallic compounds (IMC). For SnBiX alloy, lamellar Bi-Sn microstructure is visible. WLCSP12 forms hybrid joint to SAC solder ball while the solder ball does not collapse during reflow.

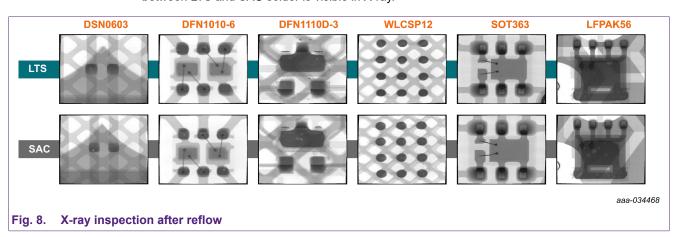

#### 5.1.4. X-ray inspection

X-ray inspection to cross check the wetting performance and solder voids. No significant difference between LTS and SAC solder is visible in X-ray.

#### Low temperature soldering, application study

## 5.2. Board level reliability

#### 5.2.1. Thermal cycling

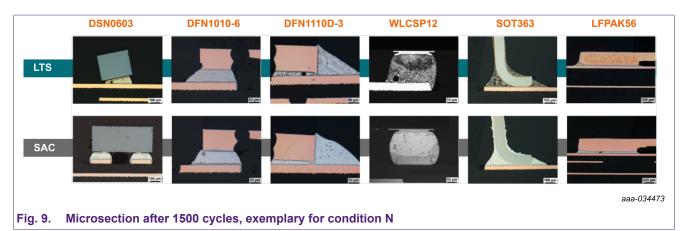

Temperature cycling test was executed (TCT / JESD22-A104D) according to condition N and G for LTS soldered samples, see <u>Table 2</u>. Electrical testing after soldering on PCB and after TCT was done with the standard tests per type. For DFN1110D-3 and WLCSP12 daisy chain samples with in-situ resistance monitoring in TCT were used.

No solder related differences could be detected between devices soldered with SAC and LTS. For LTS solder joints, grain coarsening was observed after 1500 cycles as shown in Fig. 9.

Table 2. TCT conditions according to JESD22-A104D

| Test condition | Nominal T <sub>s(min)</sub> with tolerances | Nominal T <sub>s(max)</sub> with tolerances |

|----------------|---------------------------------------------|---------------------------------------------|

| Α              | -55 (+0,-10)                                | +85 (+10,-0)                                |

| В              | -55 (+0,-10)                                | +125 (+15,-0)                               |

| С              | -65 (+0,-10)                                | +150 (+15,-0)                               |

| G              | -40 (+0,-10)                                | +125 (+15,-0)                               |

| Н              | -55 (+0,-10)                                | +150 (+15,-0)                               |

| I              | -40 (+0,-10)                                | +155 (+15,-0)                               |

| J              | -0 (+0,-10)                                 | +100 (+15,-0)                               |

| K              | -0 (+0,-10)                                 | +125 (+15,-0)                               |

| L              | -55 (+0,-10)                                | +110 (+15,-0)                               |

| M              | -40 (+0,-10)                                | +150 (+10-0)                                |

| N              | -40 (+0,-10)                                | +85 (+10,-0)                                |

In addition to required testing condition N for computing applications, TCT condition G has also been passed on all tested products soldered with LTS. Samples soldered with SAC solder paste were tested as a direct reference.

Table 3. TCT results for condition N and G

| Number       | Number of failures / total |      |       |            |      |        |      |         |      |            |      |      |

|--------------|----------------------------|------|-------|------------|------|--------|------|---------|------|------------|------|------|

| of<br>cycles | DSN0603-2                  |      | DFN10 | DFN1010B-6 |      | SOT363 |      | LFPAK56 |      | DFN1110D-3 |      | P12  |

| Cycles       | LTS                        | SAC  | LTS   | SAC        | LTS  | SAC    | LTS  | SAC     | LTS  | SAC        | LTS  | SAC  |

| 0            | 0/80                       | 0/80 | 0/75  | 0/80       | 0/80 | 0/80   | 0/80 | 0/80    | 0/60 | 0/60       | 0/48 | 0/48 |

| 500          | 0/80                       | 0/80 | 0/75  | 0/80       | 0/80 | 0/80   | 0/80 | 0/80    | 0/60 | 0/60       | 0/48 | 0/48 |

| 750          | 0/80                       | 0/80 | 0/75  | 0/80       | 0/80 | 0/80   | 0/80 | 0/80    | 0/60 | 0/60       | 0/48 | 0/48 |

| 1000         | 0/80                       | 0/80 | 0/75  | 0/80       | 0/80 | 0/80   | 0/80 | 0/80    | 0/60 | 0/60       | 0/48 | 0/48 |

| 1250         | 0/80                       | 0/80 | 0/75  | 0/80       | 0/80 | 0/80   | 0/80 | 0/80    | 0/60 | 0/60       | 0/48 | 0/48 |

| 1500         | 0/80                       | 0/80 | 0/75  | 0/80       | 0/80 | 0/80   | 0/80 | 0/80    | 0/60 | 0/60       | 0/48 | 0/48 |

#### Low temperature soldering, application study

#### 5.2.2. Drop testing

Two packages were tested, WLCSP (hybrid solder joint) and DFN1110D-3. Both packages were tested according to JEDEC specification (JESD22-B111) and drop test was performed for samples soldered with SAC and LTS solder paste.

Both packages passed the JEDEC requirements (>100 drops) and withstood >2000 drops with no occurrence.

## 6. Mechanical testing

## 6.1. Shear testing

Package shear strength was determined at 0 hour condition and after 1500 cycles TCT (condition N). Shear strength at 0 hour is found slightly higher for LTS solder compared to SAC solder joints as expected from higher mechanical strength of LTS solder reported in data sheet. All solder joints show acceptable shear strength degradation after 1500 cycles, compare <u>Table 4</u>.

All packages fulfill industry established requirements.

Table 4. Shear testing results

| Package    | Shear strength [N] |                |                |                |  |  |  |

|------------|--------------------|----------------|----------------|----------------|--|--|--|

|            | 0 cycles           |                | 1500 cycles    |                |  |  |  |

|            | LTS                | SAC            | LTS            | SAC            |  |  |  |

| DSN0603    | 5.88 ± 0.20        | 5.49 ± 0.20    | 4.81 ± 0.29    | 4.90 ± 0.78    |  |  |  |

| DFN1010-6  | 13.14 ± 0.69       | 12.26 ± 0.78   | 12.94 ± 1.57   | 11.08 ± 0.59   |  |  |  |

| DFN1110D-3 | 28.64 ± 4.51       | 24.61 ± 3.43   | 27.36 ± 3.53   | 22.95 ± 2.16   |  |  |  |

| WLCSP12    | 11.38 ± 0.69       | 12.26 ± 0.59   | 12.26 ± 0.20   | 11.77 ± 0.49   |  |  |  |

| SOT363     | 17.46 ± 1.57       | 11.57 ± 0.20   | 14.51 ± 0.69   | 11.28 ± 0.10   |  |  |  |

| LFPAK56    | 339.41 ± 32.56     | 265.56 ± 49.62 | 324.21 ± 33.24 | 278.12 ± 18.93 |  |  |  |

#### Low temperature soldering, application study

### 7. Conclusion

An extensive application study has been run on LTS assembly covering all Nexperias package platforms. Paste printing, wettability and product placement have shown comparable performance to SAC solder assembly.

After careful adjustment to LTS reflow profile, the reflow process can be run analogue to known procedures. LTS solder joints proved comparable performance, reliability has been proven by board level reliability (thermal cycling), drop test performance and joint strength in comparison to SAC solder joint.

Lower overall energy input and peak temperatures during reflow will reduce system warpage and energy consumption.

Thermal cycling was tested up to 125 °C (condition G), however customers are responsible in which application LTS will be applied.

All Nexperia packages can be soldered with no special precautions using SnBiX solder pastes.

#### 8. Further remarks

#### Stencil design

For small solder pads an optimization of stencil apertures individual per solder paste is recommended. It was found that underlying flux systems can lead to changes in release properties in stencil printing process.

#### **Electromigration**

Electromigration was not observed in this study. Care should be taken for high current transmitting packages.

#### **Units**

If not otherwise stated, all measurement units given in this document are metric units. This means that also the package nomenclature, i.e. the term "0603", refers to metric units.

## 9. Revision history

Table 5. Revision history

| Revision number | Date       | Description                                  |

|-----------------|------------|----------------------------------------------|

| 1.1             | 2022-02-22 | DSN0603 footprint drawing updated in Fig. 2. |

| 1.0             | 2022-02-18 | Initial version.                             |

Low temperature soldering, application study

# 10. Appendix 1: reflow soldering footprints

## Low temperature soldering, application study

13 / 21

Low temperature soldering, application study

## 11. Legal information

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Low temperature soldering, application study

## **List of Tables**

| Table 1. Solder paste printing details            | 5  |

|---------------------------------------------------|----|

| Table 2. TCT conditions according to JESD22-A104D | 9  |

| Table 3. TCT results for condition N and G        | 9  |

| Table 4. Shear testing results                    | 10 |

| Table 5. Revision history                         | 11 |

## Low temperature soldering, application study

# **List of Figures**

| Fig. 1. Package selection                             | 3  |

|-------------------------------------------------------|----|

| Fig. 2. Examples of footprints used                   | 4  |

| Fig. 3. Examples of drop test PCB and reliability PCB | 5  |

| Fig. 4. Reflow profile for LTS and SAC solder pastes  | 6  |

| Fig. 5. Wetting performance                           | 6  |

| Fig. 6. PCB after solder paste printing and placement | 7  |

| Fig. 7. Microsections of LTS and SAC solder joints    |    |

| after reflow                                          | 8  |

| Fig. 8. X-ray inspection after reflow                 | 8  |

| Fig. 9. Microsection after 1500 cycles, exemplary for |    |

| condition N                                           | 10 |

## Low temperature soldering, application study

## **Contents**

| 1. Introduction                             | 2  |

|---------------------------------------------|----|

| 2. LTS application study                    | 2  |

| 3. Set up and Materials                     | 3  |

| 3.1. Package selection                      | 3  |

| 3.2. Footprint and stencil design           | 3  |

| 3.3. Solder paste                           | 5  |

| 4. Reflow profile                           | 6  |

| 5. Results                                  | 6  |

| 5.1. 0 hour characterization                | 6  |

| 5.1.1. Ceramic plate test                   | 6  |

| 5.1.2. Optical inspection                   | 7  |

| 5.1.3. Microsection                         | 8  |

| 5.1.4. X-ray inspection                     | 8  |

| 5.2. Board level reliability                | 9  |

| 5.2.1. Thermal cycling                      | 9  |

| 5.2.2. Drop testing                         | 10 |

| 6. Mechanical testing                       | 10 |

| 6.1. Shear testing                          | 10 |

| 7. Conclusion                               | 11 |

| 8. Further remarks                          | 11 |

| 9. Revision history                         | 11 |

| 10. Appendix 1: reflow soldering footprints | 12 |

| 11. Legal information                       | 18 |

|                                             |    |

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 22 February 2022

<sup>©</sup> Nexperia B.V. 2022. All rights reserved