#### **Document information**

| Information | Content                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | GaN FET, drive circuit, Kelvin source (KS)                                                                                                                |

| Abstract    | This application note provides guidance on the gate drive circuit design for Nexperia's 650 V<br>Enhancement-mode GaN FETs with a Kelvin source terminal. |

### 1. Introduction

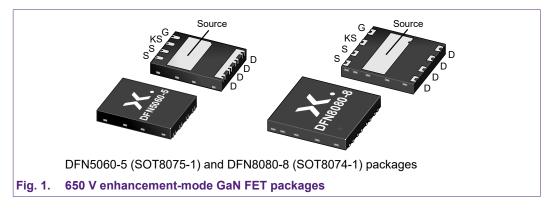

Nexperia have introduced a range of Enhancement-mode (e-mode) GaN FETs. These are available in compact, DFN leadless packages with very low parasitic inductance and feature a Kelvin source terminal to allow for decoupling of the gate drive and power loops.

This application note details some important considerations for the design of their gate drive circuitry.

# 2. 650 V e-mode GaN FET packages

Nexperia's 650 V e-mode GaN FET devices are available in 5 mm × 6 mm and 8 mm × 8 mm Dual-Flat No-lead (DFN) surface mount packages. These packages have very low parasitic inductance and feature a Kelvin source (KS) terminal, see Fig. 1.

### 3. Gate drive parameters

The key gate drive parameters for Nexperia e-mode GaN FETs and for Si MOSFETs are listed in Table 1.

| Parameter                                 | 650 V Nexperia e-<br>mode GaN FET | SI MOSFET     |

|-------------------------------------------|-----------------------------------|---------------|

| Continuous maximum<br>gate-source voltage | -1.4 V / +7 V                     | -20 V / +20 V |

| Gate-source threshold voltage             | 1.2 V - 2.5 V                     | 2 V - 4 V     |

| Recommended operating gate-source voltage | 5.5 V - 6.2 V                     | 8 V - 12 V    |

AN90041

# 4. Kelvin source KS pin

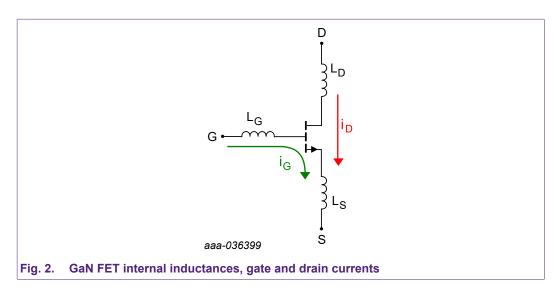

During hard switching, drain current di/dt increases rapidly. There will be a voltage drop induced on the internal source inductance  $L_S$ , which will slow down the turn-on speed, (see Fig. 2):

$$V_{GS} = V_{DRV} - L_G \frac{di_G}{dt} - L_S \frac{di_D}{dt}$$

(1)

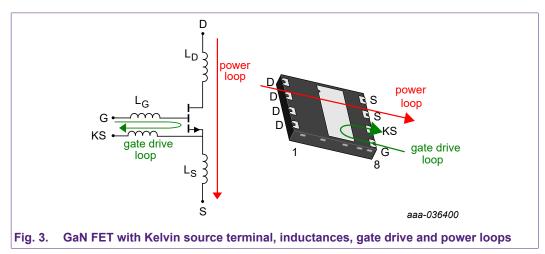

The source pins and KS pin are connected together internally, the KS pin can effectively decouple the gate drive loop and power loop to avoid the influence of power loop current change on the drive loop, see Fig. 3.

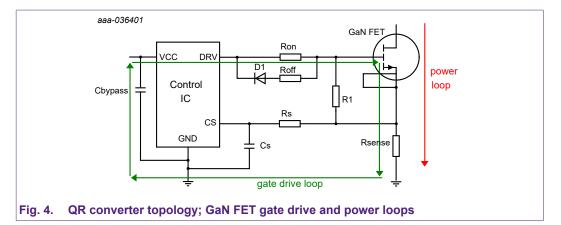

For Quasi-Resonant (QR) and other similar topologies where the controller integrates the gate drive, then the gate drive loop and the power loop are coupled together through  $R_{sense}$  and the KS pin is directly connected to the Source pin; see Fig. 4.

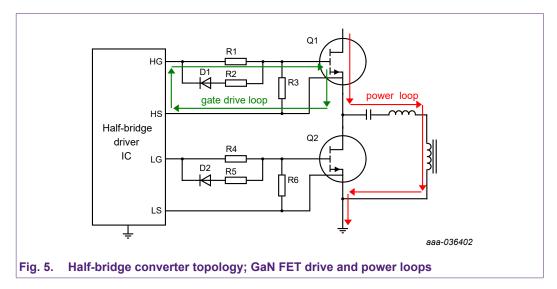

For half-bridge and other similar topologies, where the gate drive loop and power loop are independent, it should be noted that KS pin and Source pin should be separated during layout; see Fig. 5.

The circuit designer may want to consider using separate isolated gate driver ICs, such as Si8271 from Skyworks as this allows for optimising the layout for the e-mode GaN FETs.

# 5. Single GaN FET drive circuits

### 5.1. Level shift drive circuit

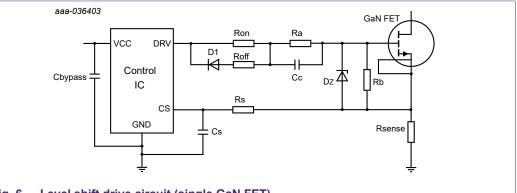

A level shifted drive circuit permits use of higher or unregulated drive voltage. Such a drive circuit is shown in Fig. 6. Table 2 gives typical component values depending on GaN FET type.

| Fig. 6. | Level shift of | drive | circuit | (single | GaN FET) |  |

|---------|----------------|-------|---------|---------|----------|--|

|---------|----------------|-------|---------|---------|----------|--|

| Symbol | Typical value   |               |               | Function               |

|--------|-----------------|---------------|---------------|------------------------|

|        | GAN080-650EBE   | GAN140-650FBE | GAN190-650FBE |                        |

|        |                 | GAN140-650EBE | GAN190-650EBE |                        |

| Ron    | 10 Ω - 1000 Ω   | 10 Ω - 560 Ω  | 10 Ω - 560 Ω  | Control turn-on speed  |

| Roff   | 2 Ω - 47 Ω      | 2 Ω - 47 Ω    | 2 Ω - 47 Ω    | Control turn-off speed |

| Dz     | 6.2 V           | 6.2 V         | 6.2 V         | Clamp the gate voltage |

| Ra     | 7.5 kΩ          | 7.5 kΩ        | 7.5 kΩ        | Voltage divider        |

| Rb     | 10 kΩ           | 10 kΩ         | 10 kΩ         |                        |

| Сс     | 330 pF - 470 pF | 680 pF - 1 nF | 1 nF - 1.5 nF | Speed-up capacitor     |

#### Table 2. Recommended driver parameters (12 V output of IC)

NOTE: driver parameters should be adjusted according to the actual design.

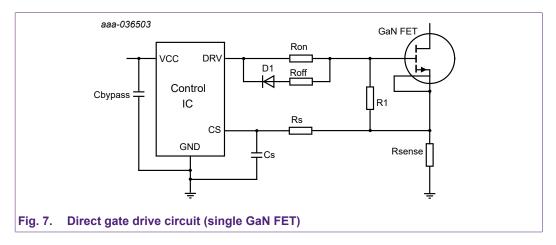

#### 5.2. Direct drive circuit

A direct gate drive circuit is shown in Fig. 7. Table 3 gives typical component values depending on GaN FET type.

| Table 3. Recommended drive | r parameters | (6 | V output of IC) |

|----------------------------|--------------|----|-----------------|

|----------------------------|--------------|----|-----------------|

| Symbol |               | Typical value               | Function      |                        |

|--------|---------------|-----------------------------|---------------|------------------------|

|        | GAN080-650EBE | GAN140-650FBE GAN190-650FBE |               |                        |

|        |               | GAN140-650EBE               | GAN190-650EBE |                        |

| Ron    | 10 Ω - 1000 Ω | 10 Ω - 560 Ω                | 10 Ω - 560 Ω  | Control turn-on speed  |

| Roff   | 2 Ω - 47 Ω    | 2 Ω - 47 Ω                  | 2 Ω - 47 Ω    | Control turn-off speed |

NOTE: driver parameters should be adjusted according to the actual design.

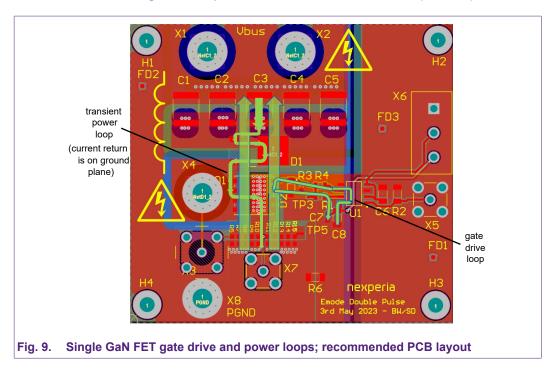

### 5.3. PCB layout precautions; single GaN FET

Correct PCB layout is critical in achieving the best performance from GaN FETs. Best design practice is:

- Minimize the drive loop by:

- a) place C7 and C8 close to the control IC

- b) place the drive circuit close to the GaN FET

- Minimize the power loop by placing C<sub>BUS</sub>, which comprises of C1 C5, inductor and the GaN FET close together.

# 6. Half-bridge level shift drive circuit

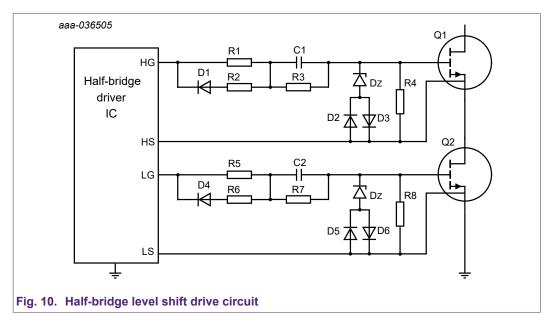

A level shifted gate drive circuit permits use of higher or unregulated drive voltage. Such a drive circuit is shown in <u>Fig. 10</u>. <u>Table 4</u> gives typical component values depending on GaN FET type.

| Table 4. Recommended | driver | narameters: | half-bridge |

|----------------------|--------|-------------|-------------|

|                      | unver  | parameters, | nan-binuge  |

| Symbol | Function                                                   | Typical value | Range                     |

|--------|------------------------------------------------------------|---------------|---------------------------|

| R1     | Control turn-on speed                                      | 390 Ω         | 10 Ω - 510 Ω              |

| D1     | Driver turn-off path                                       | PMEG6002EB    | Schottky diode (high fsw) |

| R2     | Control turn-off speed                                     | 1 Ω           | 0 Ω - 10 Ω                |

| C1     | Speed-up capacitor                                         | 2.2 nF        | 2.2 nF - 3.3 nF           |

| Dz1    | Clamp positive $V_{GS}$ when turn-on                       | 5.6 V         | 5.6 V - 6.2 V             |

| D3     | Driver turn on path                                        | PMEG6002EB    | Schottky diode (high fsw) |

| D2     | Driver turn off path,<br>increase negative V <sub>GS</sub> | PMEG6002EB    | Schottky diode (high fsw) |

| R3     | Voltage divider                                            | 7.5 kΩ        | 2 kΩ - 7.5 kΩ             |

| R4     |                                                            | 10 kΩ         | 2 kΩ - 10 kΩ              |

NOTE: driver parameters should be adjusted according to the actual design.

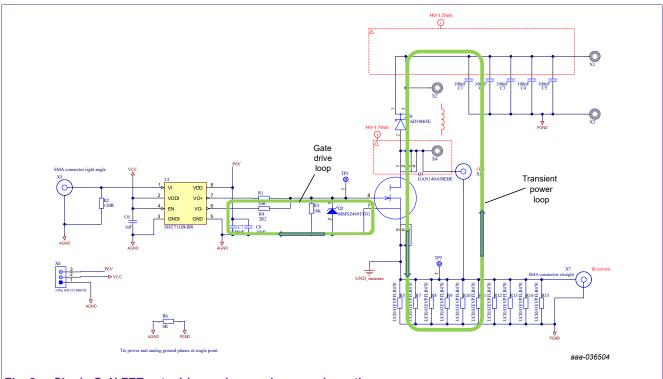

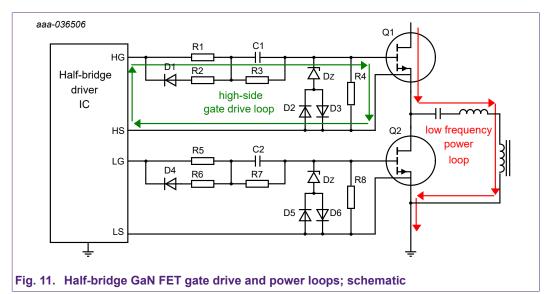

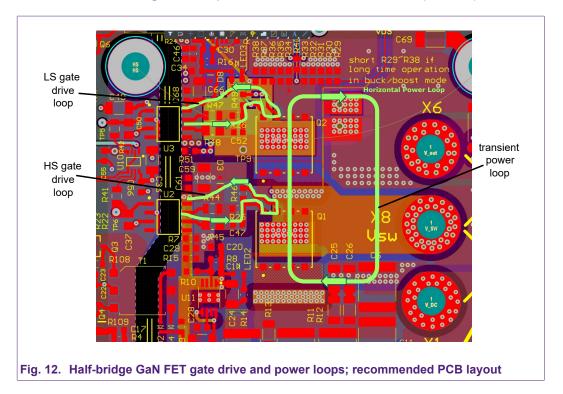

### 6.1. PCB layout precautions; half-bridge

Correct PCB layout is critical in achieving the best performance from GaN FETs.

- Use a Kelvin source design, decouple power and gate drive loops

- Place the gate drive circuit close to the GaN FET to reduce parasitic inductance

- Do not route other nets in the drive circuit area to minimize interference and cross coupling

- For the high-side, the plane side below the gate drive should be connected to the switching node.

### 7. Influence of drive resistance on EMI

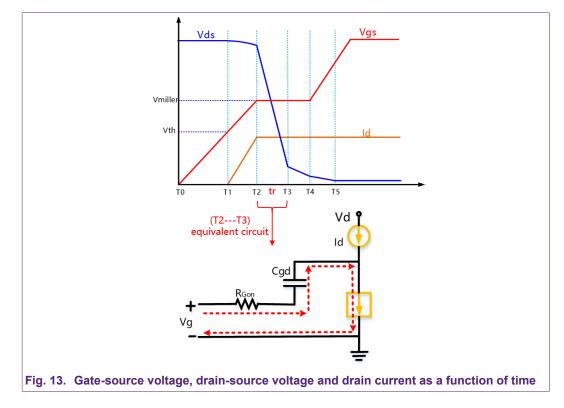

The turn-on speed, dv/dt, can be reduced by increasing R<sub>Gon</sub> appropriately, thus reducing the switching noise. As shown in <u>Fig. 13</u>, R<sub>Gon</sub> affects charging time of Cgd, the larger R<sub>G</sub>, the larger tr, the smaller dv/dt and hence the EMI noise.

Turn-off speed affects system efficiency and has little impact on EMI improvement. It is not recommended to adjust turn-off resistance  $\mathsf{R}_{\mathsf{Goff}}$ .

# 8. Suggested gate driver and controller ICs

#### Low-side gate drivers:

- Si8271 (isolated)

- LM5114

- HEY1011 (isolated)

- ACPL-P346 (opto)

Hi-Lo gate drivers:

- MDC901 (200 V)

- LMG1210 (200 V)

- Si8273 (isolated)

- NCP51530 (700 V)

Controller ICs with integrated gate drive:

- NCP1622 (PFC)

- UCC28056 (PFC)

- TEA2017AT (PFC + LLC)

- HR1211 (PFC + LLC)

- JW1515H (QR)

If a gate driver is being used with a bootstrap, then choose a bootstrap diode with low  $C_j$  and fast recovery time. For example an ES1J can be used. It is also advised to fit a 10  $\Omega$  resistor (0805) in series with the bootstrap diode

### 9. Revision history

| Table 5. Revis     | sion history |                  |

|--------------------|--------------|------------------|

| Revision<br>number | Date         | Description      |

| 1.0                | 2023-05-09   | Initial version. |

# 10. Legal information

#### Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer's third party customer's hird party customer's. Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# **List of Tables**

| Table 1. Drive difference between Nexperia e-modeGaN FET and Si MOS2 |

|----------------------------------------------------------------------|

| Table 2. Recommended driver parameters (12 Voutput of IC)            |

| Table 3. Recommended driver parameters (6 V output of IC)            |

| Table 4. Recommended driver parameters; half-bridge 8                |

| Table 5. Revision history10                                          |

AN90041

# List of Figures

| Fig. 1. 650 V enhancement-mode GaN FET packages                                             | 2 |

|---------------------------------------------------------------------------------------------|---|

| Fig. 2. GaN FET internal inductances, gate and drain<br>currents                            | 3 |

| Fig. 3. GaN FET with Kelvin source terminal, inductances, gate drive and power loops        | 3 |

| Fig. 4. QR converter topology; GaN FET gate drive<br>and power loops                        | 4 |

| Fig. 5. Half-bridge converter topology; GaN FET drive and power loops                       | 4 |

| Fig. 6. Level shift drive circuit (single GaN FET)                                          | 5 |

| Fig. 7. Direct gate drive circuit (single GaN FET)                                          | 5 |

| Fig. 8. Single GaN FET gate drive and power loops; schematic                                | 6 |

| Fig. 9. Single GaN FET gate drive and power loops; recommended PCB layout                   | 7 |

| Fig. 10. Half-bridge level shift drive circuit                                              | 7 |

| Fig. 11. Half-bridge GaN FET gate drive and power loops; schematic                          | 8 |

| Fig. 12. Half-bridge GaN FET gate drive and power loops; recommended PCB layout             | 9 |

| Fig. 13. Gate-source voltage, drain-source voltage and drain current as a function of time. | 9 |

# Contents

| 1. Introduction                             | 2  |

|---------------------------------------------|----|

| 2. 650 V e-mode GaN FET packages            | 2  |

| 3. Gate drive parameters                    | 2  |

| 4. Kelvin source KS pin                     | 3  |

| 5. Single GaN FET drive circuits            | 5  |

| 5.1. Level shift drive circuit              | 5  |

| 5.2. Direct drive circuit                   | 5  |

| 5.3. PCB layout precautions; single GaN FET | 6  |

| 6. Half-bridge level shift drive circuit    | 7  |

| 6.1. PCB layout precautions; half-bridge    | 8  |

| 7. Influence of drive resistance on EMI     | 9  |

| 8. Suggested gate driver and controller ICs | 10 |

| 9. Revision history                         |    |

| 10. Legal information                       | 11 |

© Nexperia B.V. 2023. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 9 May 2023

application note