# **APPLICATION** HANDBOOK **PROTECTION** CONCEPTS, TESTING **AND SIMULATION** FOR MODERN INTERFACES Design Engineer's Guide

nexperia

# **ESD Application Handbook**

Protection concepts, testing and simulation for modern interfaces

Design Engineer's Guide

## **Contributors**

Burkhard Laue

Jan Preibisch

Guido Notermans

Martin Pilaski

Björn Scheffler

Stefan Seider

Olaf Vogt

Dominic Wu

ESD Application Handbook Protection concepts, testing and simulation for modern interfaces Design Engineer's Guide

Copyright © Nexperia May 2019

#### www.nexperia.com

ISBN: 978-0-9934854-3-5

All rights reserved.

No part of this publication may be reproduced or distributed in any form or by any means without the prior written permission of the author.

| Introdu | uction                                    |

|---------|-------------------------------------------|

| Datash  | neet parameters of ESD protection devices |

| ESD te  | sting standards and TLP testing           |

| Princip | oles of ESD protection                    |

| SEED (  | System efficient ESD design)              |

| EMI fil | tering with common mode filters           |

| Failure | symptoms caused by ESD and surge events   |

| Interfa | ices and applications                     |

| Summa   | эгу                                       |

|         |                                           |

|         |                                           |

|         |                                           |

|         |                                           |

|         |                                           |

|         |                                           |

| Literat | cure                                      |

| Abbrev  | viations                                  |

| Index   |                                           |

| Legal i | nformation                                |

|         |                                           |

\_

| ESD | App | lication | n Hand | dboo |

|-----|-----|----------|--------|------|

|-----|-----|----------|--------|------|

### **Preface**

Nexperia is a dedicated global leader in Discretes, Logic, and MOSFET devices. We became independent at the beginning of 2017. Focusing on efficiency, Nexperia produces semiconductor components at high volume, around 100 billion annually. Our extensive portfolio of standard functions meets both the demands of today's state-of-the art applications and the stringent standards set by the automotive industry.

Through our continued efforts in innovation, reliability and support, we maintain the leading position in all our key product segments: diodes and transistors, ESD protection, MOSFETs, and logic devices. We develop and deliver benchmark solutions for today's and tomorrow's market requirements, drawing on a heritage of over 60 years' expertise in semiconductors as the former Standard Products divisions of NXP and Philips.

Our successful record in innovation is the result of varied yet streamlined R&D. We combine the latest technologies with efficient processes, helping us to serve the world's most demanding industries with world-class products.

#### **Nexperia Design Engineers Guides**

Our program of Design Engineers Guides allows us to share more technical insights with the engineering community. The first Nexperia Design Engineers Guide, released in 2017, is our MOSFET Application Handbook [1]. In the handbook, our engineers focus on how to use MOSFETs in specific applications and what the key and critical MOSFET parameters are, considering aspects like thermal conditions etc.

The program continues with this Handbook exploring ESD (Electro Static Discharge) and how to minimize the risk of damage it can cause to your circuits.

Why did Nexperia engineers decide to make a guide related to ESD?

We see that ever-increasing data rates, greater calculation power of System-on-Chips, IC miniaturization, and multiple power requirements in confined spaces, are making components and systems ever more sensitive to ESD. Another factor increasing the risk of ESD is the trend to smaller structures of semiconductor processes, because smaller voltages can damage the thinner gate oxide.

Despite all these challenges, the good news is that damages caused by ESD, or EOS (Electrical Over Stress), can be avoided or at least massively reduced with an optimized ESD protection concept. To this end, Nexperia's ESD competence can help minimize the risk of ESD damage—supporting the design community in protecting applications and products against ESD issues.

**nexperia** | Design Engineer's Guide

This "ESD Application Handbook" is a prime example of Nexperia's commitment to Standard Products, and of our endeavor to share technical insights and guidance to support our customers' needs. Inside you will find invaluable information about ESD testing and the principles of ESD protection and EMI filtering, together with application examples with an emphasis on communication bus interfaces. Due to their susceptibility to ESD damage and EMI interference, interfaces are the natural focus of this guide and it covers many popular types found in all products from mobile to automotive.

#### Olaf Vogt

Director Application Marketing Nexperia

#### **ESD Application Handbook**

4.8

### **Table of Contents**

| Chapter 1                                         |                                                                                                                                                                                                                                                                                           |                                        |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.1<br>1.2                                        | Overview of most important interfaces                                                                                                                                                                                                                                                     | 17<br>19                               |

| Chapter 2                                         | et parameters of ESD protection devices                                                                                                                                                                                                                                                   |                                        |

| 2.1<br>2.2<br>2.3<br>2.4                          | Introduction datasheet parameters Limiting values ESD maximum ratings Characteristics                                                                                                                                                                                                     | 22<br>22<br>22<br>23                   |

| Chapter 3 ESD testi                               | ing standards and TLP testing                                                                                                                                                                                                                                                             |                                        |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                   | ESD testing standard IEC 61000-4-2 Reproducibility aspects for IEC 61000-4-2 testing Surge testing standard IEC 61000-4-5 Transmission-Line Pulse (TLP) testing Very fast TLP (VF-TLP) testing                                                                                            | 28<br>31<br>33<br>35<br>37             |

| Chapter 4 Principle                               | s of ESD protection                                                                                                                                                                                                                                                                       |                                        |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.5.1<br>4.5.2 | Introduction into ESD protection choices Unidirectional ESD protection with a Zener diode Bidirectional ESD protection with Zener diodes Rail-to-rail topology with pn-diodes and Zener diode Rail-to-rail topology with SCR.  Example: Intel Z77 IC-HUB and PUSB3FR4 Latch-up scenarios. | 40<br>41<br>42<br>44<br>45<br>48<br>49 |

| 4.5.3<br>4.5.4<br>4.5.5                           | Analyzing load lines to judge the risk of latch-up scenarios Hold current and hold voltage of TrEOS protection devices Switching speed of snap-back ESD protection                                                                                                                        | 50<br>51<br>52                         |

| 4.6<br>4.7                                        | Findings for ultra-high-speed interfaces and SoCs                                                                                                                                                                                                                                         | 54<br>56                               |

Layout and placement hints for an effective ESD protection ...... 57

| Chapter 5 SEED (Sy                                                 | stem efficient ESD design)                                                                                                                                                                                                                        |                                  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7 | Creation of a system model  PCB model.  Verilog-A  Diode Clamp Model  Clamp model with snap-back  Clamp model with snap-back and additional kink  Clamp model with snap-back and current hysteresis  Dynamic voltage overshoot during triggering. | 60<br>61<br>63<br>64<br>67<br>68 |

| 5.1.8<br>5.1.9<br>5.1.10                                           | TLP current source  TLP IEC 61000-4-2 source (gun model)  Verilog-A code examples                                                                                                                                                                 | 69<br>70<br>73                   |

| Chapter 6                                                          | ring with common mode filters                                                                                                                                                                                                                     |                                  |

|                                                                    |                                                                                                                                                                                                                                                   |                                  |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                    | Introduction to common mode filters  Common mode filters combined with ESD protection  Differential passband  Commode mode rejection  ESD protection performance of combined  CMF and ESD protection                                              | 80<br>80<br>82                   |

|                                                                    | ymptoms in electronic components y ESD and surge events                                                                                                                                                                                           | 86                               |

| Chapter 8                                                          | es and applications                                                                                                                                                                                                                               |                                  |

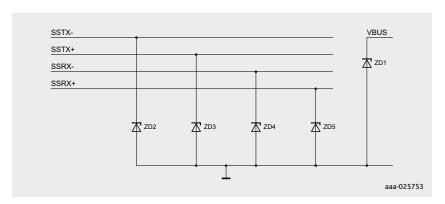

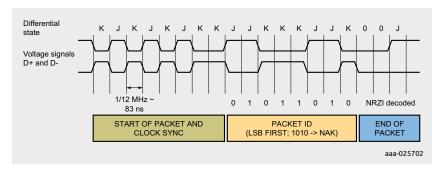

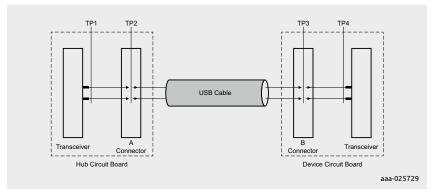

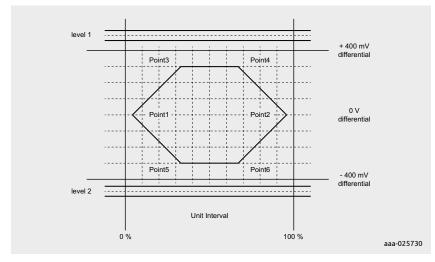

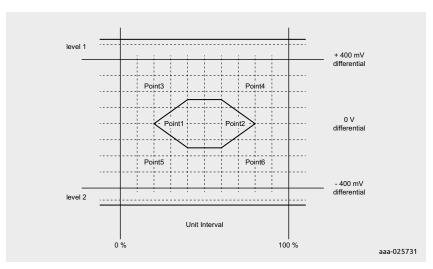

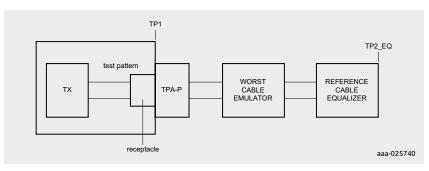

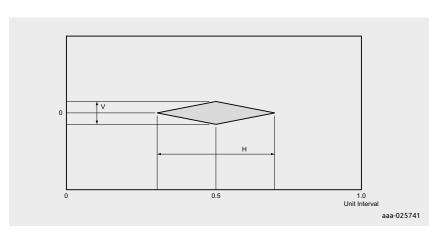

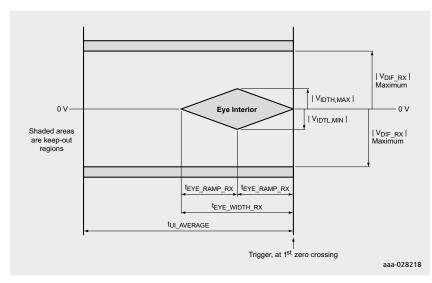

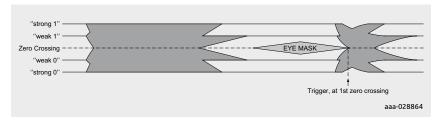

| 8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.2            | USB standards, data speeds and coding methods USB 1.0 and USB 2.0 interfaces USB 2.0 eye diagrams USB 3.0 and USB 3.1 interfaces USB 3.0 eye diagrams USB Type-C HDMI interfaces                                                                  | 92<br>98<br>103                  |

| 8.2.1<br>8.2.2<br>8.2.3                                            | Introduction to HDMI interfaces                                                                                                                                                                                                                   |                                  |

| 8.3        | MIPI interface                            |

|------------|-------------------------------------------|

| 8.3.1      | Introduction to MIPI interfaces           |

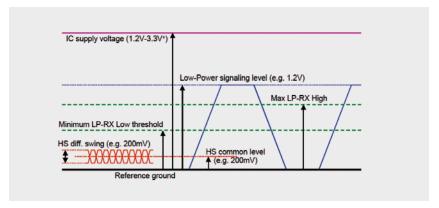

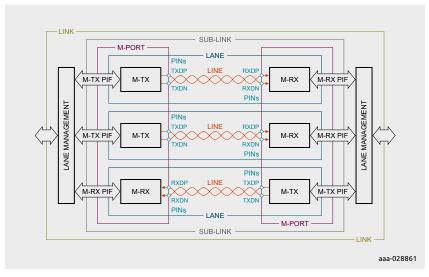

| 8.3.2      | MIPI D-PHY                                |

| 8.3.3      | MIPI M-PHY                                |

| 8.3.4      | MIPI C-PHY                                |

| 8.4        | In-vehicle Networking (IVN)               |

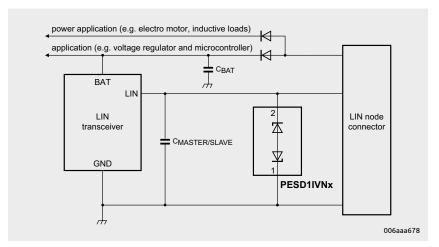

| 8.4.1      | Introduction to In-vehicle Networking     |

| 8.4.2      | LIN Interface                             |

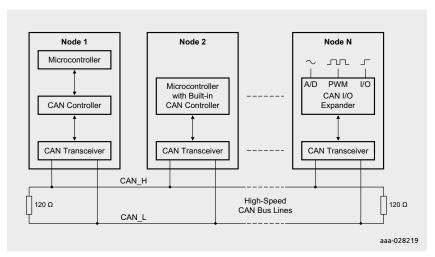

| 8.4.3      | CAN Interface                             |

| 8.4.4      | CAN FD Interface                          |

| 8.4.5      | FlexRay Interface                         |

| 8.4.6      | BroadR-Reach and 100BASE-T1 Interface     |

| 8.4.7      | Automotive Multimedia Interfaces          |

| 8.5        | Antenna interfaces                        |

| 8.5.1      | Properties of antenna interfaces          |

| 8.5.2      | ESD protection for antenna interfaces     |

| 8.6        | Supply line protection with TVS diodes    |

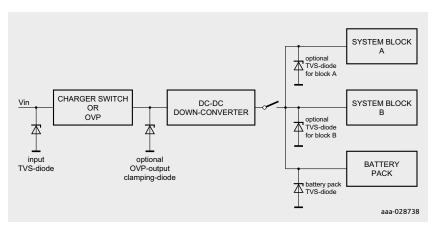

| 8.6.1      | Introduction to supply line protection    |

| 8.6.2      | Pulse standards                           |

| 8.6.3      | TVS operation                             |

| 8.6.4      | Typical applications in a portable device |

|            |                                           |

| Chapter 9  |                                           |

| Summary    | <b>,</b>                                  |

|            |                                           |

| Literatur  | <b>e</b>                                  |

|            |                                           |

| Abbrevia   | tions                                     |

|            |                                           |

| Index      | 154                                       |

|            |                                           |

| Legal info | ormation                                  |

# Chapter 1 Introduction

Introduction

Shrinking silicon geometries allow more complex electronic content to be squeezed into small spaces. With these new silicon processes oxide lavers have become thinner and the gates of embedded FETs are therefore more vulnerable to surge events. High voltage events of up to 30 kV peak voltage with about 100 ns overall pulse width resulting from electrostatic discharges (ESD) must be considered as well as surge events with a longer pulse width of about 60 µs and less extreme voltage levels.

Often, designers can no longer rely on the internal ESD protection structures of the system chips. Internal ESD protection is good enough to protect the components during the assembly process in a mostly ESD safe environment. It does not protect against ESD events seen in the field. External protection cannot be seen as a luxury or left out.

In computing, consumer, and mobile products, super-speed interfaces conquer the market where huge quantities of data are transferred or copied in a short time. The automotive industry introduced many Electronic Control Units (ECUs) that are connected via networks exposed to ESD strikes and surge events potentially induced from high-current switching over long cables, load dump conditions, or voltage changes from cold car cranking.

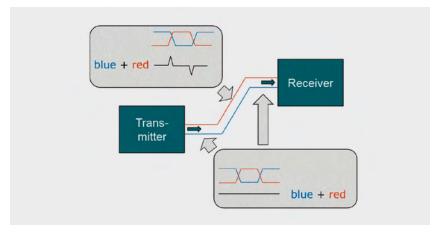

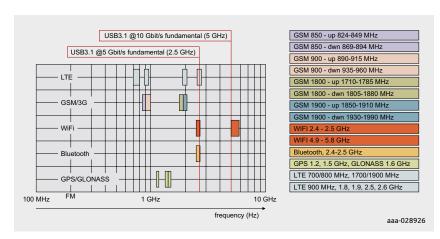

All modern high-speed and super-speed interfaces use differential data signals and operate with reduced signal levels. High data speed, up to 20 Gbit/s, requires a carefully designed PCB layout to maintain signal integrity. This can be achieved by proper impedance matching, avoiding unacceptable losses and reflections. Various electromagnetic interference (EMI) aspects also need to be considered when sensitive GSM, WiFi, or GPS receivers are located close to potentially radiating high-speed interfaces.

This handbook provides information about the physical layers for selected data interfaces used in mobile, computing, and consumer applications as well as for interfaces that can be found in automotive applications. These layer specifications are relevant for the selection of adequate ESD protection, to maintain signal integrity, and to choose the most suitable ESD diode topology respecting signal levels and the structure of drivers and receivers.

Findings for latest generation super-speed interfaces and practical knowledge how to get these extremely sensitive interfaces properly protected with high system level robustness are presented. Furthermore, different ESD and surge protection topologies and their major application areas are discussed.

The key parameters found in datasheets are explained in detail and how to choose a suitable component for a design based on this information. Various testing standards have been established to allow reproducible testing and qualification of electronic components and products. The most important testing methods are discussed in this handbook and how to use the 'new' Transmission-line pulse (TLP) testing method. It introduces a scientific selection process for ESD protection devices, overcoming the time-consuming trial and error testing that does not necessarily find the best solution.

In addition, the handbook introduces the so-called System efficient ESD design (SEED) methodology to simulate ESD behavior of ESD protection devices and system chip interfaces as individual blocks as well as in combination to judge if the two components will fit together and are safe against ESD and surge events.

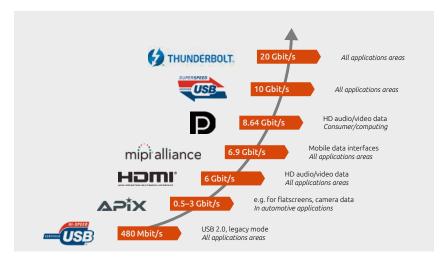

# 1.1 Overview of most important interfaces

Interfaces with external connectors accessible to users require the highest attention to be safe against electrostatic discharge and surge events. The most important wired high-speed multimedia interfaces in the market are shown in Figure 1. An ongoing increase in the maximum supported data rate can clearly be seen. This is not achieved with more parallel data connections but with a higher bit rate on the data lines, which has a significant impact on the requirements for ESD protection as discussed in depth in Chapter 8.

Figure 1 | Multimedia Interfaces

Introduction

- Universal Serial Bus (USB) specifications USB 2.0 and its successor USB 3 generation 1 and 2, have dominated all application areas like mobile communication, computing, consumer, and automotive infotainment. USB interfaces certainly require ESD protection because of the regularity of connecting and disconnecting devices by end-customers. More details can be found in Section 8.1.

- APIX is found in automotive application as flat-screen or camera data interface.

- High Definition Multimedia Interface (HDMI) is one of the major video/ audio interfaces in consumer applications. It has achieved a high relevance for computing applications for monitor connection, supporting video and audio data transfer in parallel. Resolution in terms of pixels per frame and quantization of video data has increased over time. HDMI data lines are DC-coupled which makes this interface somewhat special for ESD protection as discussed later in this handbook. For more details see Section 8.2.

- Display Port (DP) is an alternative connection for HDMI and important for the computing market, it also supports high display resolutions.

- MHL (Mobile High definition Link), with similarities to HDMI, is used in some mobile devices and TV sets but as yet has not gained significant market share.

- Mobile Industry Processor Interface (MIPI) is mainly an internal interface for mobile processors to cameras, memories, displays and sensors. It has a high relevance in smartphones and although an internal interface, ESD protection can be found in many designs. More details can be found in Section 8.3.

- Thunderbolt interfaces are gaining importance with the introduction of Type-C connectors. Type-C connection can support different data interface standards as a new hardware platform of a miniaturized connection. Following the fully established USB interface Thunderbolt can gain market share in the computing market. It has the very high physical data speed of 20 Gbit/s. Usually, ESD protection suitable for USB super speed lines can be applied for Thunderbolt as well.

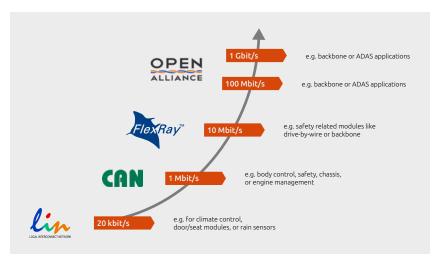

Figure 2 | Automotive Interfaces

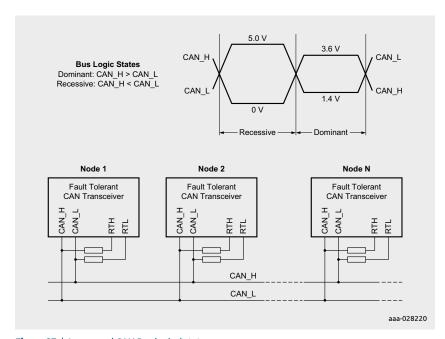

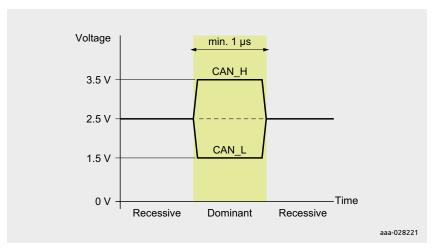

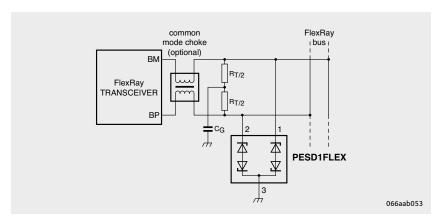

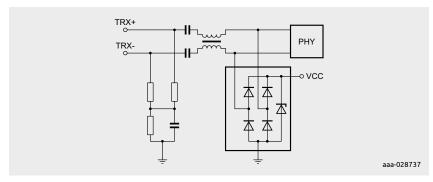

Figure 2 shows dedicated data interfaces for automotive applications including LIN. CAN and FlexRay. Like the multimedia interfaces data speed constantly increase to support the growing electronic content in modern cars. A more detailed overview is provided in Section 8.4.

In addition to the digital interfaces mentioned above, ESD protection of antenna inputs is a special application area discussed in Section 8.5 of this handbook, along with surge protection of DC supplies in Section 8.6.

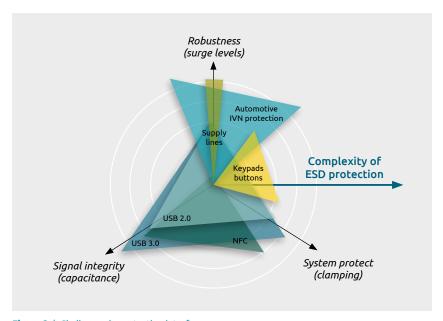

# 1.2 Three key parameters for a suitable ESD and surge protection

Regardless of the application or interface, when choosing an ESD protection strategy, there are three essential parameters. The first is a high robustness of the protection device itself against ESD and surge events. Another requirement is a low clamping voltage with a low dynamic resistance. A low dynamic resistance stands for a steep I-V-curve of the protection, so that clamping voltage does not increase much if surge current is increased. These requirements are extremely important to achieve a high system level robustness - the primary goal of why ESD and surge protection is applied.

As a third key parameter, a low capacitance of the ESD protection device is required if high data rates need to be handled. Low capacitance is key to maintain excellent signal integrity. From a design perspective, trying to maximize one parameter can result in a deterioration of another. Figure 3 shows the three discussed key parameters and their relevance for different application areas.

Figure 3 | Challenges in protecting interfaces

Under the name TrEOS Protection Nexperia is offering an ESD protection technology that combines benchmark values for all three key parameters – deep snap-back, low dynamic resistance and high ESD robustness with very low capacitance. This technology is ideally suited for super-speed data lines such as RX/TX lines of USB 3.2 or Thunderbolt interfaces and to protect very sensitive SoCs.

# Chapter 2

# Datasheet parameters of ESD protection devices

## 2.1 Introduction to datasheet parameters

To select suitable ESD protection devices, development engineers have to compare key parameters that can be found in vendor datasheets. In this chapter the most important key parameters and their relevance for a well operating interface are described. Furthermore, the signal integrity has to be maintained to ensure that receiver circuits in digital interfaces can sample the incoming data without errors. The following chapters are clustered like the information in most datasheets for ESD protection devices by Nexperia.

## 2.2 Limiting Values

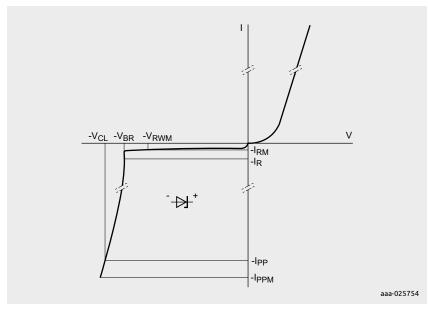

$V_{RWM}$  is the standoff voltage of a protection device. It indicates the maximum operating voltage range for which leakage current is below a specified value  $I_{RM}$ .  $V_{RWM}$  has to be equal to or higher than the maximum voltage expected on a signal line.

$I_{\text{PPM}}$  is the maximum surge current that a device can withstand if an IEC 61000-4-5 [2] pulse with an 8/20 µs timing is applied. This value gives an indication of the robustness of ESD devices if they are exposed to higher pulse energy, see Chapter 3.3.

For the junction temperature  $T_j$ , a maximum value is given which usually is 150°C. Beside this information, an ambient temperature range  $T_{amb}$  and storage temperature  $T_{sto}$  can be found with minimum and maximum limits.

## 2.3 ESD maximum ratings

V<sub>ESD</sub> gives the maximum voltages that an ESD protection device can withstand, in compliance with IEC 61000-4-2 [3], see Chapter 3.2. The limits in kV are given for positive and negative ESD test pulses. The datasheets give limits for contact discharge testing as well as for air discharge testing. For low capacitance protection devices, the air discharge rating is not significantly higher than the contact discharge rating. Designers should rely on the contact discharge rating because this is much better in reproducibility. The ESD rating does not indicate if a protection device will provide good protection for an interface. It has no correlation to the ESD system robustness that can be achieved. In the best case, the overall system robustness is limited by the ESD robustness of the ESD protection device.

However, this is not the case in most applications if sensitive interface pins have to be protected. If the system chip is damaged with an  $8 \, \text{kV}$  ESD pulse in a system test, it does not help that an ESD diode with a  $+/-30 \, \text{kV}$  rating was applied. A low clamping protection diode rated for e.g.  $15 \, \text{kV}$  can be the far better choice.

#### 2.4 Characteristics

The diode capacitance  $C_d$  is an important parameter related to the maximum frequency of a signal line. The value is given for a test frequency of usually 1 MHz and no bias; sometimes, additional values with bias voltage are provided. A bias voltage leads to lower  $C_d$  values because the capacitance of internal pn-junction, decrease with reverse voltage.

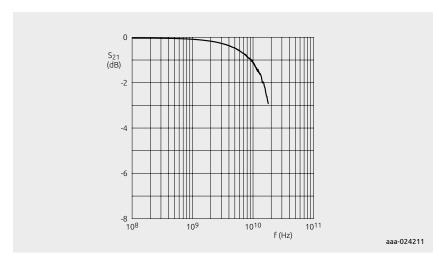

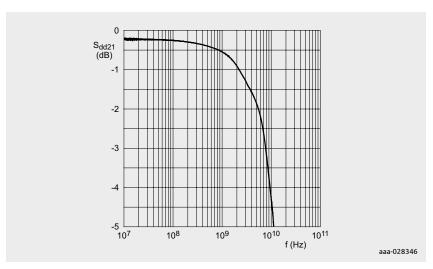

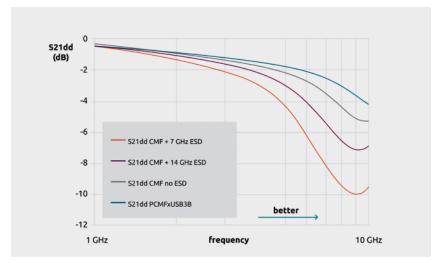

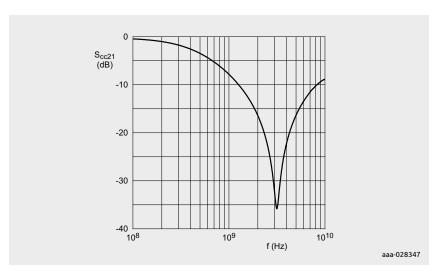

$f_{-3dB}$  is the -3 dB frequency of the insertion loss tested at a sine-wave generator with  $50\,\Omega$  output resistance. Figure 4 shows an example for an insertion loss curve with a -3 dB cut-off frequency of about 17 GHz. For data interfaces, at least the fundamental wave should pass without big losses. To achieve steeper transitions, it is essential to have a significant spectral component for the 3rd harmonic as well.

Figure 4 | S<sub>21</sub> insertion loss curve of PESD3V3Z1BSF

$V_{BR}$  is the breakdown voltage of a protection device. It is tested with a current-driven set-up in which 1 mA test current is driven through the DUT. The voltage across the DUT is  $V_{BR}$ .

For a topology similar to an ordinary Zener diode, this parameter is of practical interest as it indicates the voltage at which leakage current will reach 1 mA. However, for ESD protection that has a snap-back topology but not static behavior, V<sub>BR</sub> can be misleading. ESD protection devices with an open-base topology have very low leakage currents below 1 mA before the trigger voltage is reached. The current-driven test approach for V<sub>BR</sub> forces such devices into snap-back. In this case  $V_{BR}$  is lower than the trigger voltage and  $V_{RWM}$  can be higher than  $V_{BR}$  in principle.

$I_{RM}$  is the leakage current at  $V_{RWM}$ . It is typically extremely low, at 1 nA and a maximum rating of 50 nA.

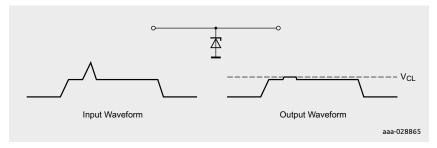

$V_{CL}$  are clamping voltages for IEC 61000-4-5 pulses for different peak currents  $I_{DD}$ . Usually  $V_{CL}$  is given for the limiting  $I_{DD}$  value and additional lower values.

R<sub>dvn</sub> is the so called dynamic resistance. For modern devices this parameter is defined by the steepness of the TLP curve for TLP pulses with 100 ns pulse width at  $I_{PP} \sim 16 \, \text{A}$ . The lower the dynamic resistance of a protection device, the better is the clamping performance. This is because the clamping voltage increases less for rising surge currents. In many datasheets, dynamic resistances are given based on IEC 61000-4-5 (8/30 us pulses) test results. The value is derived from an Ipp (peak current) versus clamping voltage curve for such a test. When comparing dynamic resistances, attention has to be paid to the test method, because the values are not identical for the two approaches due to the significantly higher energy of IEC 61000-4-5 pulses towards TLP testing.

#### S-parameters

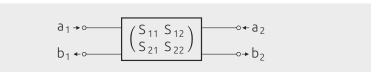

A scattering, or S-parameter, matrix is a mathematical approach that quantifies how RF energy propagates through a multi-port network [16]. The S-parameter matrix allows the properties of a complicated network to be described as a simple black box with n ports. The matrix for a network with n ports contains n<sup>2</sup> coefficients, each of them representing a possible path.

S-parameters are complex numbers containing real and imaginary parts, or a magnitude and phase part. The network changes both the magnitude and phase of the incident signal. S-parameters are defined for a given frequency and a defined system impedance  $Z_0$ , which is 50  $\Omega$  for datasheets and Nexperia laboratory testing. S-parameters are measured over a chosen frequency range and vary over frequency, as Figure 4 shows with the example of an  $S_{21}$  parameter curve.

S-parameters are usually depicted in a matrix format. The number of rows and columns is equal to the number of ports. For the S-parameter  $S_{mn}$  the n subscript stands for the port that is excited, as input port. The m subscript stands for the output port. This means  $S_{11}$  describes the reflection on port one: It is the relativ signal amplitude that is reflected. Parameters in the S-matrix diagonal are the reflection coefficients, while those located off the diagonal are called transmission coefficients. They describe how the network reacts at a port if it is excited with an incident sinewave from another port. The parameter  $S_{21}$  is often referred to as insertion loss.

S-parameters describe the response of an n-port network to a signal incident to any or all of the ports.

Figure 5 | 2-port network with 4 nodes and direction indication arrows

Figure 5 shows a 2-port network. The signal at a port, for example port 1, can be thought of as the superposition of two waves running in opposite directions. By convention, each port is shown as two nodes so as to give a name and value to these opposite direction waves. The variable  $a_m$  represents a wave incident to port m and the variable b<sub>0</sub> represents a wave reflected from port n. From the matrix formula below the following equations are valid for the four S-parameters of the 2-port network:

$$\begin{pmatrix} b_1 \\ b_2 \end{pmatrix} = \begin{pmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{pmatrix} \cdot \begin{pmatrix} a_1 \\ a_2 \end{pmatrix}$$

$$S_{11} = \frac{b_1}{a_1}$$

,  $S_{12} = \frac{b_1}{a_2}$ ,  $S_{21} = \frac{b_2}{a_1}$ ,  $S_{22} = \frac{b_2}{a_2}$

# Chapter 3

# ESD testing standards and TLP testing

## 3.1 ESD testing standard IEC61000-4-2

IEC 61000-4-2 defines test methods and configuration environment for ESD robustness testing [3]. It is commonly used to certify electronic equipment. Devices must be protected against ESD using components that can clamp and resist the high voltages, as defined by the respective IEC standards. The robustness of these devices has to be checked and guaranteed.

Most electrostatic discharges occur unnoticed by users but can seriously damage gate oxides of MOSFETs used in the data path of most interfaces. In some cases, a small flash indicates that a sudden electrical discharge has occurred. The aftereffects are high leakage currents and malfunction of input and output circuits.

Contact and rubbing of different materials causes seperations of charger by means of the socalled triboelectric effect. Furthermore, electrostatic induction leads to a redistribution of electrical charge in an object caused by the influence of nearby charges.

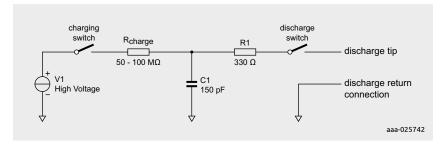

Please note that when ESD protection components are mounted in a product to protect some of its sensitive parts, the behavior of these components must be tested in their final application environment. ESD pulses are generated with an ESD gun that consists of an adjustable high voltage source with maximum of 30 kV. A 150 pF capacitor is charged through a resistor with 50 to 100 M $\Omega$ , using a charging switch. The capacitor is discharged through a 330  $\Omega$  resistor when the discharge switch is closed. Figure 6 shows a basic ESD pulse generator schematic.

Figure 6 | ESD pulse generator according to IEC 61000-4-2

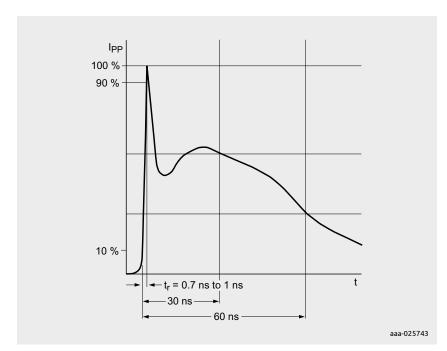

Figure 7 shows the shape of the IEC 61000-4-2 discharge current waveform of the described generator. The curve behaves in the following way:

- 1. The pulse rises within 0.7 to 1 ns.

- 2. The first spike reaches its peak current with the peak value  $I_{pp}$ .

- 3. The pulse then declines within about  $80\,\mathrm{ns}$  including a shoulder-shape curve.

Most of the surge pulse energy is carried by the shoulder. The first spike stresses the target with high voltage and high current, but with less energy because duration is short. Two methods are used for ESD testing: The contact measurement method and the air discharge measurement method.

The contact measurement method is the recommended IEC 61000-4-2 method for ESD protection components and is set-up as described below:

- The ground pin of the component is connected. The ESD gun is connected to ground via the discharge return connection as well.

- The tip of the ESD gun is connected to the contact of the device under test (DUT).

In contrast to the system level testing described in IEC 61000-4-2, the test procedure of ESD protection devices does not employ resistors ( $2 \times 470 \, k\Omega$ ) in the return path. The contact discharge connection allows good reproducibility of test results. Further details on the test procedure can be found in [5].

Table 1 lists current values for predefined IEC 61000-4-2 levels, i.e. ESD levels 1 to 4, for respective peak currents, 30 ns and 60 ns.

Figure 7 | IEC 61000-4-2 waveform

Table 1: ESD test waveform parameters

| ESD level | voltage | first peak current,<br>+/–10% | Current (+/– 30%)<br>at 30ns | Current (+/– 30%)<br>at 60ns |

|-----------|---------|-------------------------------|------------------------------|------------------------------|

| 1         | 2 kV    | 7.5                           | 4                            | 2                            |

| 2         | 4 kV    | 15                            | 8                            | 4                            |

| 3         | 6 kV    | 22.5                          | 12                           | 6                            |

| 4         | 8 kV    | 30                            | 16                           | 8                            |

Table 2 shows the definition of IEC 61000-4-2 ESD levels with the related minimum discharge voltages for contact discharge testing.

Table 2: ESD levels as defined in IEC 61000-4-2

| ESD level | contact discharge | air discharge |

|-----------|-------------------|---------------|

| 1         | 2 kV              | 2 kV          |

| 2         | 4 kV              | 4 kV          |

| 3         | 6 kV              | 8 kV          |

| 4         | 8 kV              | 15 kV         |

For air discharge the tip of the ESD gun is narrowed slowly towards the target until a flash strikes over. The results depend very much on air humidity, speed of decreassing distance between target and gun, and shape of electrodes. Generally this test shows low reproducibility. Often, corona discharge can be noticed without a flash if one of the two electrodes has a sharp end. In such a case, the stress on the ESD device is very low and does not lead to usable results. For the gun side a tip with a round end is defined for air discharge, whereas the tip for contact discharge has a sharp end. The air discharge waveform has a less steep rising edge and the surge pulse peak values are lower. Therefore, air discharge robustness is higher than, or equal to, contact discharge.

Please note that technical documents must be regarded with skepticism if air discharge ratings are presented with much higher values than for contact discharge. Often, a factor of roughly 2 like the ESD level 4 definition in Table 2 is presented. Please note that the voltage levels do not imply each other, but are just categorizations for practical usage. Moreover, the levels defined in [3] refer to system level testing rather than device level. It is a proven fact that for low capacity ESD protection devices the air discharge robustness is a few kV higher or the same compared to contact discharge robustness. For this reason air discharge testing is discouraged not recommended, because it is much more difficult to do it correctly and, if done correctly, it provides exactly the same results as contact testing [32].

Human Metal Model (HMM) test uses the same waveform as defined for ESD guns in standard and supports  $50\,\Omega$  terminated testing of ESD protection products and interfaces. The defined termination guaranties good reproducibility of test results as known from TLP tests.

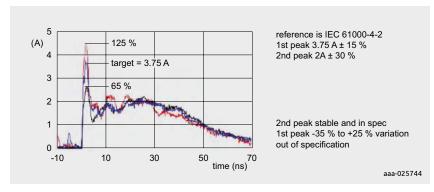

# 3.2 Reproducibility aspects for IEC 61000-4-2 testing

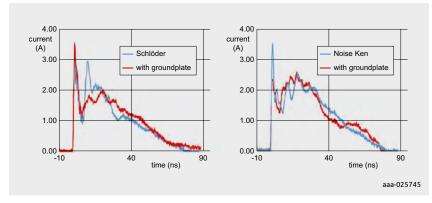

Figure 8 shows that the ESD gun waveform is not fully reproducible: Here, a NoiseKen gun<sup>1</sup> is shooting in repeat mode at a target while a high frequency current probe<sup>2</sup> is measuring the current waveform. The second peak, which is located on the shoulder behind the first peak, is stable and is well within the IEC 61000-4-2 specification. However, the voltage of the first peak shows a big variation from +25% to -35%. If target systems are sensitive to the first peak of an ESD event, test results can show a big spread which can lead to wrong decisions being taken in the selection process of protection devices. Guns of other manufacturers show simular behaviour.

<sup>1</sup> ESS2000AX

<sup>2</sup> F-65 current probe 1 MHz-1 GHz from Fischer Custom Communications

**ESD testing standards and TLP testing**

Figure 8 | IEC 61000-4-2 waveforms with NoiseKen ESS2000AX gun

Please note that the grounding condition has a big impact on the voltage level of the first peak as well. If there is no proper ground close to the DUT, a small residual capacitance to ground occurs. If this is the case, the first peak loses its height and can mostly disappear. Figure 9 shows the current waveforms of two ESD gun<sup>3</sup> types with and without proper grounding. In set ups without proper grounding test results are unreliable.

Figure 9 | Waveform comparison for ESD gun with and without proper grounding

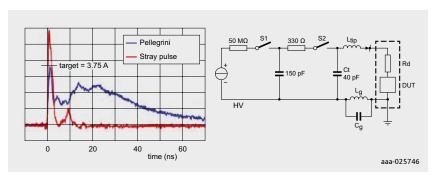

Another risk in ESD gun testing arises when the gun is not safely connected to the DUT for contact discharge. Figure 10 shows the circuit of an ESD gun with a parasitic tip capacitance C<sub>r</sub> of roughly 40 pF, which is significant compared to the nominal 150 pF of the ESD gun.

3 A SESD 30.000 from Schlöder and a ESS2000AX from NoiseKen

When a triggered gun misses the target or when the charge moves across the switch S2. the C<sub>F</sub> charge can discharge into the DUT with almost no series impedance. This is why the first peak of this socalled stray pulse can exceed the regular pulse by a factor of 2, as illustrated by the red curve in the diagram.

In conclusion, if a system is tested that shows an ESD sensitivity on the first peak, unsafe ESD gun connection can lead to damage at a comparatively low testing voltage, wrong test results, and ESD device selection. A propper test setup is essential to ensure reproducibility of ESD testing. More details about system level ESD testing of high-speed interface boards can be found in [16] and [33].

Figure 10 | Stray pulses after the target was missed

## 3.3 Surge testing standard IEC 61000-4-5

Testing according to IEC 61000-4-5 [2] uses much wider test pulses than in the ESD testing according to IEC 61000-4-2 [3] discussed in the previous chapter. The energy of surge pulses, as defined in [2], is much higher. Consequently, an ESD protection part has to dissipate more heat. The IEC 61000-4-5 standard approach simulates surge events, for instance in scenarios like power supply voltage overshoots created by load changes or overshoots caused by the plug-in procedure of chargers.

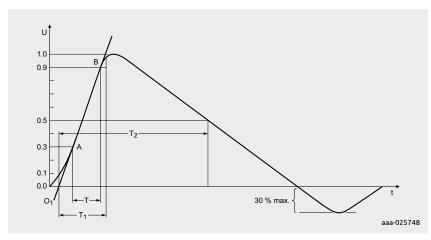

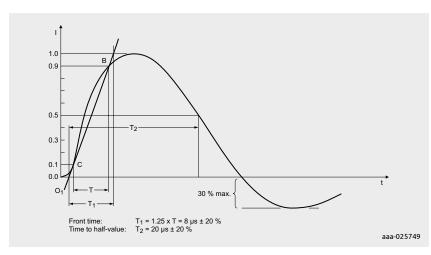

Table 3 lists key waveform data of IEC 61000-4-5 surge pulses. For the short-circuit condition of the surge generator, see Figure 12,  $8\,\mu s$  rise time and  $20\,\mu s$  fall time to 50% voltage level are defined and is well known as the 8/20 µs surge test.

Table 4 lists the relation between selected values of the peak voltage for the open circuit condition, see Figure 11, and the peak current for the short circuit case. Output impedance of a surge generator is considered to be  $2\Omega$ .

Table 3: Surge pulse waveform parameters

| operating mode        | Front time in µs | time down to 50% value in µs |

|-----------------------|------------------|------------------------------|

| open-circuit voltage  | 1.2 +/- 30%      | 50 +/- 20%                   |

| short-circuit current | 8 +/- 20%        | 20 +/- 20%                   |

Table 4: Open-circuit peak voltage and related peak current for the short-circuit

| open circuit peak voltage +/– 10% | short-circuit peak current +/– 10% |

|-----------------------------------|------------------------------------|

| 0.5 kV                            | 0.25 kA                            |

| 1.0 kV                            | 0.50 kA                            |

| 2.0 kV                            | 1.00 kA                            |

| 4.0 kV                            | 2.00 kA                            |

Figure 11 shows the waveform for the open circuit condition, whereas Figure 12 depicts the surge pulse waveform for the short circuit scenario.

Figure 11 | IEC 61000-4-5 waveform for open circuit condition

Figure 12 | IEC 61000-4-5 waveform for short circuit condition

IEC 61000-4-5 test results deliver important data sheet parameters for ESD and surge protection devices:

- Maximum surge current—I<sub>PP</sub>

- Peak power—Ppp

- Clamping voltage—V<sub>CL</sub>

- Dynamic resistance— $R_{dyn}$ —derived from the steepness of  $V_{CL}$  versus  $I_{PP}$  curves

## 3.4 Transmission-Line Pulse (TLP) testing

TLP is a comparatively new measurement technique used to characterize complete interfaces or ESD protection components [4,5].

TLP is a short-duration rectangular pulse in a controlled impedance environment of  $50\,\Omega$ , which improves test accuracy and measurement reproducibility. TLP characterizes performance attributes of devices under stresses that have a short pulse width and fast rise time. Low duty cycles prevent heating.

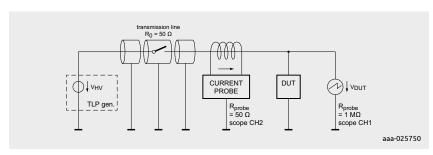

The TLP test environment shown in Figure 13 can be described as follows: a generator charges a  $50\,\Omega$  transmission line with a pre-adjusted voltage. The switch is closed and the energy is applied to the DUT. The current into the DUT measured by a current probe, while the voltage at the DUT is monitored using a high-speed oscilloscope. The pulse length, rise, and fall times can be changed at the generator. Typically, the standard pulse applied has a 100 ns duration and rise and fall times of 10 ns each. The minimum programmable transition times are 300 ps.

**ESD testing standards and TLP testing**

Figure 13 | TLP test set-up

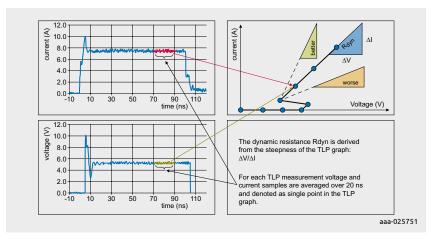

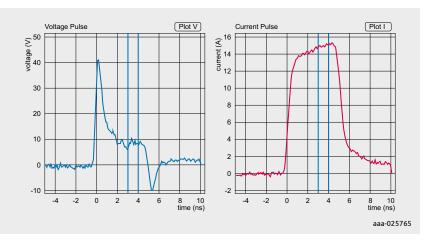

The TLP test is performed starting gradually from low pulse voltages to higher voltages, with a pre-defined step width. As shown in the TLP measurement voltage and current traces depicted in Figure 14, the voltage and current samples are averaged for a window of 20 ns. Located in a temporal window from 70 ns to 90 ns within the 100 ns test pulse, the window-based method eliminates noise. Also, the window's location ensures that the system is settled so that run-in effects like overshoots are eliminated. Each measurement result becomes a point on the TLP graph that shows a TLP I-V characteristic, i.e. the TLP-curve.

The steepness of the TLP curve  $\Delta V/\Delta I$  is the  $R_{dvn}$ , which is an important parameter for selecting ESD and surge protection devices.

TLP testing can be done with ESD protection devices, and with interface pins of complete systems with and without ESD protection. From the derived TLP curves conclusions can be drawn as to which protection device is suitable to protect a product safely and reliably.

Figure 14 | TLP curve derived from TLP test events

## 3.5 Very fast TLP (VF-TLP) testing

A very similar testing method to TLP is very-fast TLP (VF-TLP) [6]. The major differences being the 1 to 10 ns duration of the test pulses and the short rise and fall times of 100 to 600 ps.

Figure 15 shows the VF-TLP measurement set-up. Due to short pulses, the current is not measured with a current probe. Instead, it is derived from measuring incident and reflected voltages separately with an oscilloscope. This is done in a similar way to time domain reflection (TDR) measurement. The current in the DUT is calculated using:

$I_{DUT} = I_{incident} + I_{reflected} = \frac{V_{incident} - V_{reflected}}{50.0}$

Delay TLP Generator Pickoff 50 Ω I<sub>DUT</sub> (t) V<sub>DUT</sub> (t) Oscilloscope aaa-025752

Figure 15 | Test set-up for VF-TLP measurement

In conclusion, VF-TLP tests provide a good indication for determining the switching speed of ESD protection devices. The small pulse length is useful because the impact of the first overshoot of an ESD event on a target system can be investigated.

In contrast to that, the 100 ns standard TLP pulses are roughly equivalent to the energy of a complete ESD pulse, in which the larger proportion of energy is carried in the wider second shoulder of the pulse.

# Chapter 4

# Principles of ESD protection

### 4.1 Introduction into ESD protection choices

Several different approaches can be used to protect electronic devices against ESD and surge events.

#### · Narrow gap or spark gap approach

An easy and inexpensive approach is to add a narrow gap from ground to signal line. Whenever a bigger ESD event occurs, an air discharge limits a high voltage pulse.

Spark gap components operate on the same physical principal. Thus, adding a spark gap to a signal line is a straightforward approach. The disadvantage of this kind of ESD protection is comparatively poor performance in terms of the achieved clamping voltage that has a slow turn-on time and a very high trigger voltage. The average dielectric air strength is about 3.3 kV/mm. This is why a spark gap is not a good protection device choice for modern high-speed interfaces.

#### Use of varistors

Varistors are often used for ESD protection. These parts are made with ceramic ZiO grain material in a mixture with other metal oxides. Varistors have a symmetrical non-linear I-V curve which shows a high resistance for lower voltages. When the varistor reaches breakdown voltage, it starts conducting. Varistors deteriorate after exposure to surge events. Older generation varistors show a very high first spike in IEC 61000-4-2 testing, however newer generation varistors are much improved. Unfortunately, the clamping voltage for the second shoulder remains significantly higher compared to silicon-based solutions. This is why varistors are not the first choice for protecting modern system chip interfaces.

#### Silicon-based ESD protection

Silicon-based ESD protection are the preferred choice as they show no degradation after surge events, as long as the specified limits are obeyed. Several topologies are available that provide ESD protection ranging from a simple topology, as presented in Figure 17, to more sophisticated topologies, as presented in several scenarios on the subsequent pages.

Silicon-based ESD protection is recommended with best and lowest clamping voltage performance, as explained on the subsequent pages of this section.

# 4.2 Unidirectional ESD protection with a Zener diode

A very plain topology is a Zener diode placed between ground and signal line, as depicted in Figure 16. Surge pulses are clamped to a voltage  $V_{CL}$  that is based on the following  $V_{CL}$  equation:

$$V_{CL} = V_{BR} + I_{PP} \cdot R_{dyn}$$

Figure 16 | ESD protection based on Zener diodes

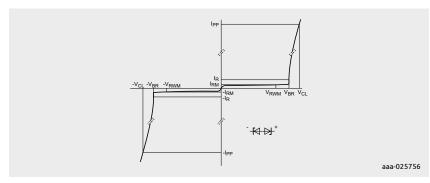

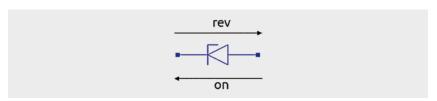

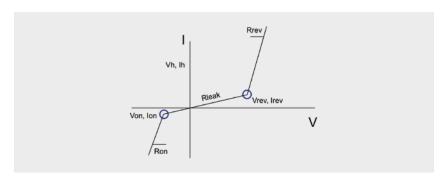

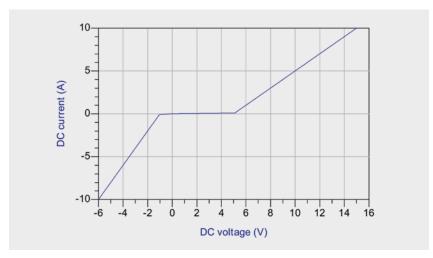

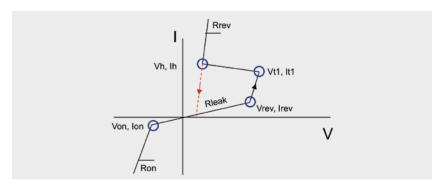

Figure 17 shows a typical Zener diode I-V curve. The left side of the curve shows the Zener diode in the reverse bias region. The current is very small, as long as the test or operating voltage remains below  $V_{RWM}$ .  $V_{RWM}$  is referred to as stand-off working voltage. Below this voltage, reverse leakage current is smaller than the specified  $I_{RM}$ . When the voltage increases, current increases suddenly, at which the avalanche region begins; marked by the breakdown voltage  $V_{BR}$ . The breakdown voltage is measured in a current-driven test set-up that pushes 1 mA through the diode.

The right side of the curve shows the Zener diode in the forward bias region. The current is picking up if the voltage exceeds  $V_F$ . Negative surge pulses are clamped to relatively low voltages ( $V_F$  –0.7 V). The described topology forms a unidirectional protection.

A Zener diode creates a unidirectional protection for an interface, clamping at considerably low voltages for negative surge events above  $V_F$ , as well as clamping voltage—according to the  $V_C$  equation—for positive surge events.

Figure 17 | I-V curve of a Zener-diode or avalanche type ESD protection diode

# 4.3 Bidirectional ESD protection with Zener diodes

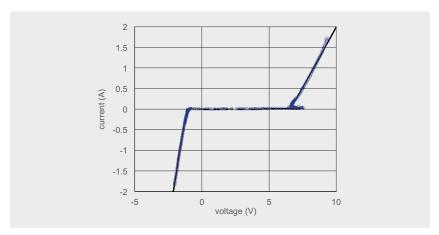

If two Zener diodes with opposite directions are connected in a series, as shown in Figure 18, a bidirectional ESD device is created. If the two diodes are identical, the I-V curve is symmetrical, as depicted in Figure 19.

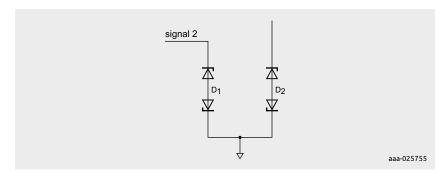

Figure 18 | ESD protection with a bidirectional ESD protection diode.

Figure 19 | I-V curve of a bidirectional ESD diode with a simple avalanche behavior

The calculation of the clamping voltage is the same as the equation for the reverse direction of unidirectional ESD diodes:

$$V_{CL} = V_{BR} + I_{PP} \cdot R_{dyn}$$

, with  $V_{BR} = V_{BR1} + V_{F}$

The  $V_F$  value is adding a portion to  $V_{BR}$  and the reverse breakdown  $V_{BR1}$  of the other diode. Bidirectional ESD protection has to be applied to interfaces that operate with positive and negative voltage ranges. For example, analog audio signals. Most digital interfaces that only operate with positive voltages can be protected with a unidirectional solution. Anyhow, many designers make use of bidirectional ESD protection. The SOC are exposed to much higher negative clamping voltages for negative ESD strikes. This should be avoided if possible because it can badly affect the system level robustness.

This problem is particularly relevant if a system chip has to be protected against negative surge events with higher energy and longer pulse duration, as specified in the IEC 61000-4-5 standard. If the surge protection addresses only ESD pulses according to IEC 61000-4-2, a relatively insensitive chip might be sufficiently protected with a bidirectional topology.

When designing low capacitance ESD protection components it can be helpful to choose this structure with two ESD diodes in series because the parasitic capacitance is lower compared to a unidirectional device, as the below commonly known equation shows:

$$C_d = \frac{C_1 \cdot C_2}{C_1 + C_2}$$

Another reason for choosing bidirectional ESD diodes is that the mounting direction is not important.

# 4.4 Rail-to-rail topology with pn-diodes and Zener diode

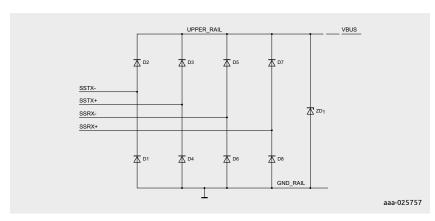

Figure 20 shows an ESD protection environment with a rail-to-rail topology:

- From each signal line, one pn-diode is connected to the upper rail, while another pn-diode is connected from the signal node to the ground rail (GND)

- A Zener diode is connected between ground and upper rail

- Positive surge pulses push the energy through the upper diodes towards the upper rail

- Negative surge pulses push the energy through the lower diodes towards ground

- To improve the ESD performance, the upper rail can be connected to the supply voltage

The Zener diode functions as a clamping device and limits the voltage of positive surge events. If the upper rail is connected to a supply line or Vbus, current can flow into the supply as well where, typically, capacitors can damp incoming pulses. As a negative side effect, microcontroller circuits can show soft fails generated by the supply voltage overshoot created.

The rail-to-rail structure allows a very robust structure with a high capacitance of the Zener diode. The pn-diodes are comparatively small, with a small parasitic capacitance.  $C_d$  on the signal line is roughly twice the capacitance of the pn-diode, assuming that the top and ground rail works like a short circuit for RF components. This short is caused by the Zener diode's big capacitance and the comparatively big capacitors connected to the supply line.

Figure 20 | ESD protection with rail-to-rail topology

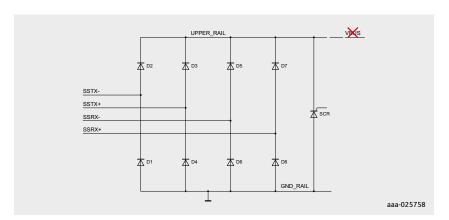

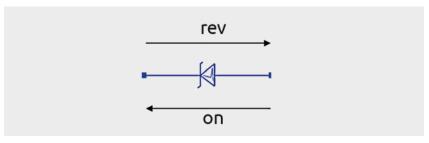

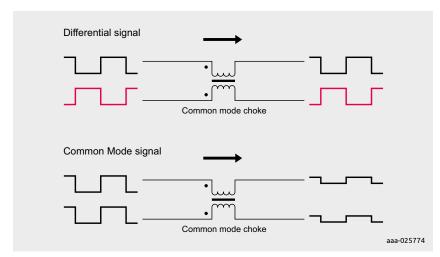

### 4.5 Rail-to-rail topology with SCR

Figure 21 contains a modification of the conventional rail-to-rail topology. Instead of a Zener diode, an silicon-controlled rectifier (SCR) is put between upper rail and ground. If the voltage of the upper rail exceeds a specified trigger voltage, the SCR switches into on-state and connects the two rails. If the current through SCR falls below a specified hold current, the SCR switches off again and becomes high-ohmic again.

Please note that when this protection topology is used, a supply line cannot be connected to the upper rail or to the signal inputs. In the case of a trigger event, the SCR would not return into the off-state because a DC-supply can easily provide a constant current above the hold current I<sub>hold</sub>. The ESD protection component could be damaged or the supply line stays in a short-circuit condition.

Figure 21 | Rail-to-Rail ESD protection device with SCR

The advantage of the SCR-based approach is that very low clamping voltages can be achieved for surge events. The turn-on effect is often called snap-back because the voltage at the ESD protection device jumps down from a trigger voltage towards a low voltage in on-state. The snap-back voltage can be designed to drop lower than the high state voltage of a signal line and below  $V_{\rm RWM}$ . Although this appears to be a conflict, in most cases it does not create a problem. Many high-speed interfaces are designed to be free of DC content in the data stream. Therefore, the data lines do not stay in single-ended high-state. Once the signal toggles back to low-state the hold current or hold voltage condition for the SCR is violated and the ESD component switches off again.

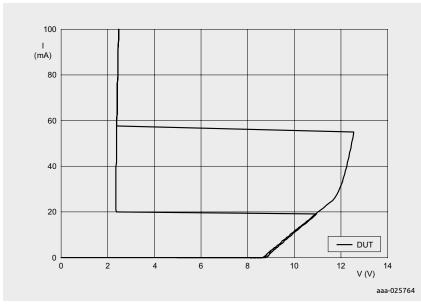

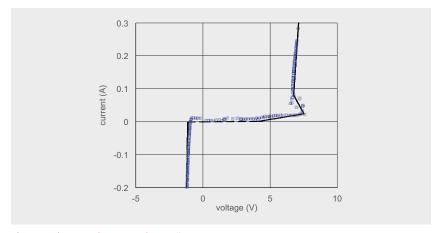

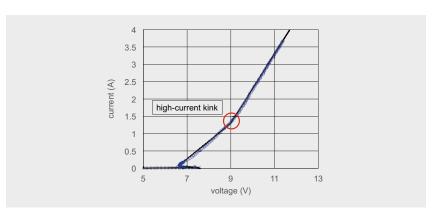

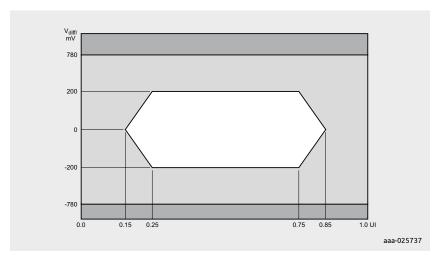

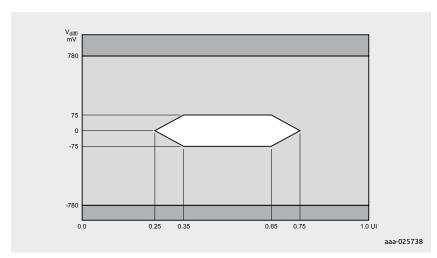

Beside testing with a suitable I-V curve tracer, the snap-back characteristic can best be evaluated with a TLP test. Figure 22 shows a TLP curve of PESD3V3Z1BSF as an example for a TrEOS snap-back device. The device triggers at about 9 V and snaps back to 2.5 V. From there the TLP I-V-graph shows a mostly linear curve with a steepness of  $R_{dyn} = 0.19 \Omega$ .

Figure 22 | TLP-Curve example of PESD3V3Z1BSF

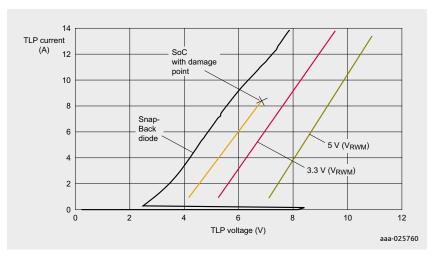

Figure 23 compares typical TLP curves with each other, as described below.

- Green TLP curve: ESD protection products that are based on an avalanche effect clamping topology that are specified for operating with  $V_{RWM}$  5V to 5.5 V. They have a breakdown voltage  $V_{RR}$  that is equal to or greater than 7 V.

- Red TLP curve: Parts that are specified for operating below or equal V<sub>PMM</sub> 3.3 V have a lower breakdown voltage of typically equal or greater than 5 V. Thus, clamping voltages are lower and more current of the surge event is dissipated in the protection device compared to the 5 V type.

- Yellow TLP curve: TLP testing can also be applied to interface pins and complete electronic products. Modern ICs often show TLP curves that start at relatively low voltages. As soon as the pulse voltage is raised, they show a steep increase of current, which is due to a low dynamic interface resistance.

Please note that many ICs can only cope with a relatively low maximum TLP current. This can be  $I_{PP} = 5 A$ , for instance.

• Black TLP curve: Shows a deep snap-back topology example. By adding an SCR, very low clamping voltages after turn-on of the device can be realized. A big portion of the surge energy is dissipated in the ESD protection and the overall system level robustness is improved. The destruction voltage of the yellow curve is reached for much higher currents.

In conclusion, effective ESD protection requires a TLP curve for the ESD protection device that is located left of the TLP curve of the SoC. The curve must show a high steepness with no cross point to the SoC curve. In this way it can be ensured that most of the surge current flows through the protection; and only a lower current through the IC input structure. The point where the system is destroyed is shifted to higher currents. An ideal TLP curve would be perpendicular ( $R_{dvn} = 0 \Omega$ ), where the clamping voltage does not increase with the surge current.

With an avalanche topology, the breakdown voltage cannot be decreased any further down into the operating voltage range of the interface without causing leakages. This means that further improvement for a low clamping voltage can be driven in the direction of a perpendicular TLP curve only. However, dynamic resistance decrease has technological limits. Therefore snap-back topology allows lowest clamping voltages and highest system protection levels for sensitive interfaces.

Figure 23 | TLP-Curves of avalanche type ESD diodes with VRWM5 V (green), Vrwm 3.3 V (red), SoC (yellow with point of destruction) and snap-back ESD diode

#### 4.5.1 Example: Intel Z77 IC-HUB and PUSB3FR4

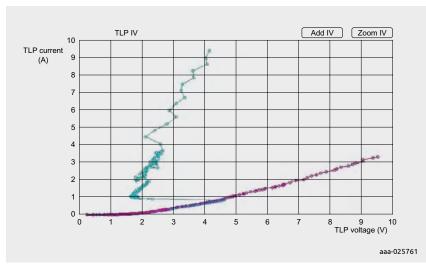

Figure 24 compares two ESD protection scenarios. TLP is measured at the input pins of a test PCB. The magenta curve shows the TLP curve of an Intel Z77 IC-Hub RX input, while the cyan TLP curve shows the same device with PUSB3FR4 as ESD protection:

- The magenta TLP curve shows a relatively high dynamic impedance of around 3  $\Omega$ . The SoC manages up to 3.5 A pulse current.

- The cyan TLP curve shows the characteristics achieved with the 4-line PUSB3FR4 protection device. The curve shows an I-V characteristic with a deep snap-back and a steep linear line after the ESD protection device has triggered. Most of the surge current flows via the PUSB3FR4 and not into the SoC. This is achieved due to a very low dynamic resistance, which is only one tenth of the system chip resistance. Thus, most of the surge energy is dissipated in the protection device. The system chip is therefore protected very effectively, with an excellent level of system robustness. An extremely high TLP current would be required again to reach the TLP voltage for destruction for the SoC (about 9.5 V).

Figure 24 | TLP-Curve Rx line Intel ICH BD82Z77 stand-alone (magenta) and combined with PUSB3FR4 (cyan)

#### 4.5.2 Latch-up scenarios

If a snap-back device is triggered, a latch-up can happen if the on-state current is higher than the hold current of the ESD protection device. However, most ESD protection devices withstand the current arising from this condition: Nexperia parts were tested in latch-up with 100 mA for several hours without showing any damage or degradation. If an interface is affected, a soft fail occurs but no hardware fail. For many interfaces, the snap-back device automatically returns to its off-state once the affected data line is in single-ended low state.

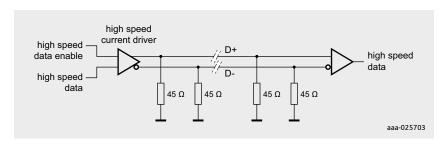

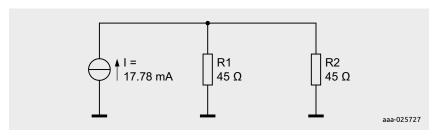

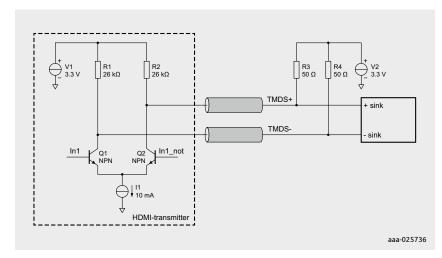

An HDMI interface requires some attention with respect to possible latch-up conditions. The HDMI interface topology is given in Figure 80. Many HDMI input circuits are designed with active silicon circuits for the  $50 \Omega$  pull-up resistors. HDMI interfaces have to be safe for short-circuits on the TMDS lines according to HDMI standard requirements. To avoid overheating of active pull-up resistors, the pull-up voltage is shortly removed whenever a short is detected at the TMDS lines. This mechanism releases a latch-up condition.

Please note that Transmission Minimized Differential Signal (TMDS) lines begin data transfer after connection is established. The risk of ESD strikes is much higher during the connecting process of a cable, and very unlikely to happen at a cable with fully established connection. In practice, no known field returns are caused by latch-up failures with HDMI interfaces.

The maximum latch-up current for HDMI can be calculated in a straightforward way. The pull-up voltage can be 3.5 V (3.3 V + 5%) as maximum and the pull-up resistors can have a minimum resistance of 45  $\Omega$  (50  $\Omega$  –10%). Assuming a snapback voltage of 1.24V, the maximum potential latch-up current can be calculated as 50 mA. If the hold current of the ESD protection is smaller than this value, there is a potential risk for the interface to hang-up. More Details on HDMI interfaces can be found in Chapter 8.

I<sup>2</sup>C bus interface is another example that can be affected by latch-up conditions. The maximum high-state current of this interface is defined by the selected pull-up resistors. There is no potential problem if the high-state current is lower than the hold current of the ESD protection device. If it is higher, the I<sup>2</sup>C-bus master detects the hand-up situation on the bus and can initiate a power cycle to release the bus again.

#### 4.5.3 Analyzing load lines to judge the risk of latch-up scenarios

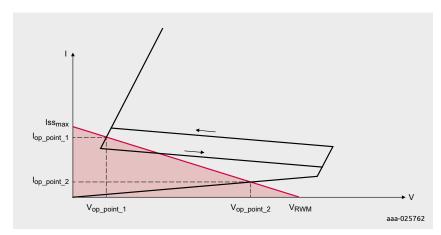

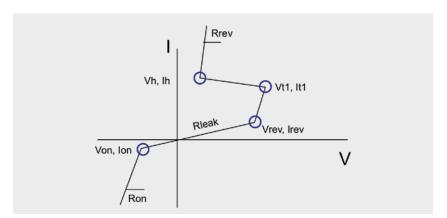

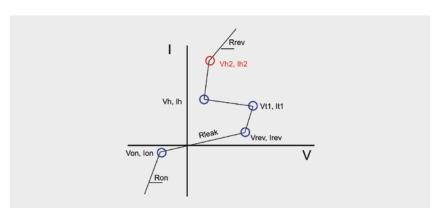

Figure 25 shows an I-V characteristic of an interface output driver with a detailed I-V diagram of a snap-back ESD device.

The load line of an interface starts at a short circuit current on the y-axis. It shows a linear decay toward the open circuit case where the x-axis is crossed at the data line drive voltage  $V_{DD}$ .

The ESD protection I-V curve shows a hysteresis. The arrows mark which trace is valid for the direction of test voltage change. If the voltage increases, the snapback triggers as soon as the trigger voltage is reached. From that point onwards, the curve continues on a steep on-state path. When the testing current is decreased below Ihold, the ESD protection device turns off again, utilizing the lower paths, shown in the diagram, to leap to higher voltage. In similar scenarios as shown in the diagram, an ESD strike can produce a latch-up condition. An interface can get stuck at operating point 1. To be safe from a latch-up scenario, the load line of an interface should only cross the I-V curve of the protection device once.

Figure 25 | I-V characteristic of interface output driver; snap-back ESD protection device

In an established USB Type-C connection (pin assignment Table 17), the configuration channels CC1 or CC2 are connected to  $V_{conn}$ .  $V_{conn}$  is a 5 V DC supply. Sideband usage signals SBU1 and SBU2 can be overlaid by a DC. This applies to analog audio use cases in which the DC supplies amplifiers. A snap-back ESD diode that can snap below a DC level of a signal line should not be selected for these cases. Of course,  $V_{Bus}$  is suitable for snap-back devices in this context.

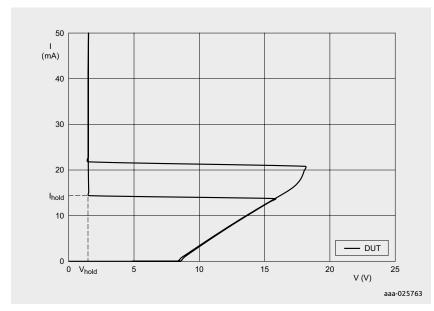

#### 4.5.4 Hold current and hold voltage of TrEOS protection devices

In Figure 26 the I-V curve shows measurement results with a current-driven curve tracer for the unidirectional TrEOS product PESD5V0C1USF. The curve delivers a hold current of I<sub>hold</sub> 16 mA and a hold voltage of V<sub>hold</sub> 1.4 V. A hysteresis curve can be seen, as explained in the previous section. Ihold and Vhold can be derived from the current and voltage point at the lower left corner of the hysteresis area.

Figure 26 | I-V curve of unidirectional PESD5V0C1USF with hysteresis characteristic

The I-V curve of Figure 27 shows measurement results with a current-driven curve tracer for the bidirectional TrEOS product PESD5V0H1BSF. The curve delivers the same hold current as for the unidirectional part, which is  $I_{hold}$  +/- 16 mA. The hold voltage is  $\pm V_{hold}$  2.2 V. The hold voltage  $V_H$  is higher because of the bidirectional solution's series structure, which also includes an additional  $V_E$  value of 0.8 V of a diode that is driven in forward direction.

Figure 27 | I-V curve of PESD5V0H1BSF with hysteresis characteristic

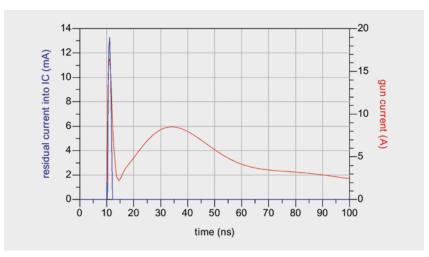

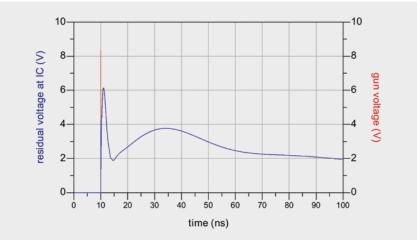

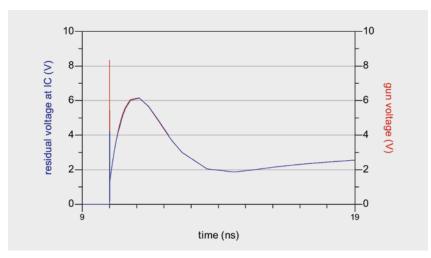

#### 4.5.5 Switching speed of snap-back ESD protection

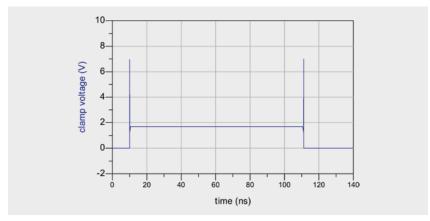

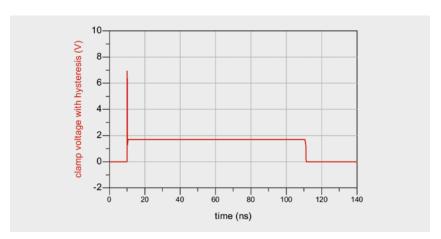

An effective ESD protection limits a surge pulse to a safe clamped voltage within a short time without excessive and wide overshoots. This temporal behavior, as shown in Figure 28, can be evaluated with a VF-TLP test by analyzing the voltage traces of the single test events.

Figure 28 shows a voltage and current trace of a VF-TLP test for a PESD5V0H1BSF at a peak current  $I_{PP}$  of 15 A, with pulse width 5 ns, and rise and fall time of 600 ps. The voltage trace shows a narrow overshoot. After device turn-on, the comparatively low clamping voltage is reached [34].

Figure 28 | VF-TLP (5 ns/200 ps) voltage and current traces PESD3V3Z1BSF at I<sub>PP</sub> = 15 A

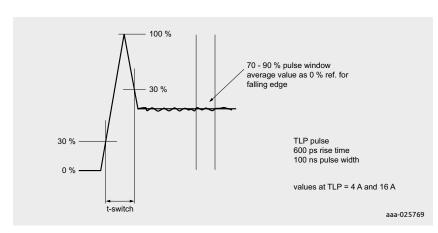

Figure 29 shows a way how the turn-on time can be derived from a VF-TLP voltage scope trace. The average value in the 70% to 90% window is taken as zero percent reference value for the falling edge. The TrEOS devices turns on within approximately 1 ns, as Figure 28 shows. The switching time interval is derived from the 30% values at the rising and falling edges of the voltage overshoot in the scope trace.

For many products in the market, the turn-on time is relatively long. This prevents the device from switching on at all in a VF-TLP pulse. Turn-on times of about 10 ns are often encountered. Devices that show this weakness cannot protect very sensitive high-speed interfaces and cannot achieve the required system robustness.

Figure 29 | Measurement of switching time (turn-on time) based on VF-TLP test pulse

# 4.6 Findings for ultra-high-speed interfaces and SoCs

As stated in Section 3.2, tests with ESD guns have a widespread destruction level, should the first overshoot be critical for the system chip. Tests with HMM, TLP and VF-TLP pulses deliver much more stable and reproducible results.

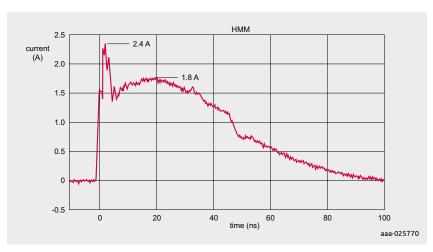

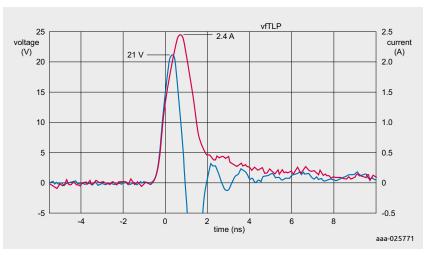

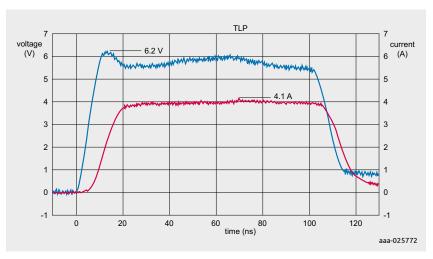

Figure 30 shows an HMM current trace marking the limit of a sensitive SoC for this kind of test pulse. The IC was tested without an external ESD protection. The peak current of the first overshoot is 2.4A. The current peak of the second shoulder is 1.8 A. In Figure 31 such a device with VF-TLP pulses is tested. The device is destroyed when 2.4 A as peak current is reached; like in the first overshoot in the HMM test above. The peak voltage for this pulse is 21 V.

In an additional test, as shown in Figure 32, the interface chip is tested with a 100 ns wide TLP pulse. The destruction level is 4.1 A, which is much more than the value of the HMM pulse shoulder. This means the SoC device is damaged by the first overshoot of an ESD strike. Note that the damage does not occur during the shoulder, where the higher amount of energy of the overall surge pulse is located. For the latest generation of ESD-sensitive ICs an effective ESD protection must limit the first overshoot effectively, which is achieved by a fast reaction time and low clamping.

Figure 30 | HMM current curve and fail level for a sensitive 10 Gbit/s USB 3.1 SoC

Figure 31 | VF-TLP fail level for this interface

Figure 32 | TLP fail level for this interface

### 4.7 Effect of parasitic inductance

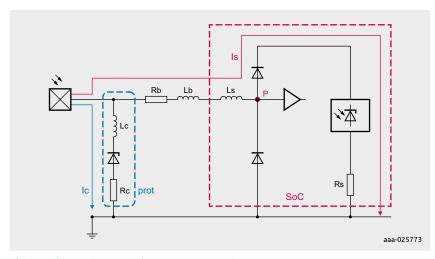

Figure 33 shows an equivalent circuit for an IC input with an additional external ESD protection that can be used to simulate a surge event:

- The IC has a rail-to-rail ESD protection structure for the input pin.

- The upper diode is connected to a voltage clamping element with an additional serial resistance of RS.

- LS and RB represent the inductances of the IC bond wires or internal connections and the parasitic inductance of the signal routing on the PCB.

- RB is the serial ohmic impedance between interface and IC input.

- The external ESD protection component is represented by a voltage clamping element, a serial resistor Rc and a parasitic capacitance Lc.

In order to achieve effective ESD protection and good system level robustness, it is helpful that Lc is very small in relation to Lb+Ls. This improves the damping of the first overshoot of an ESD strike.

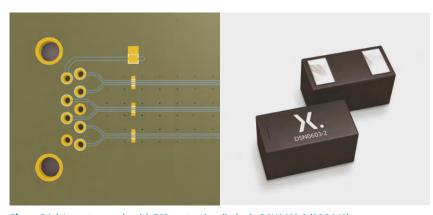

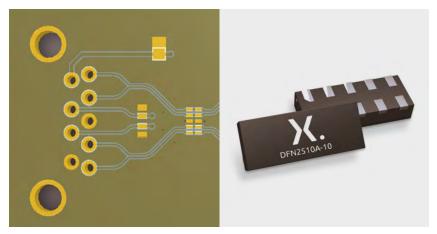

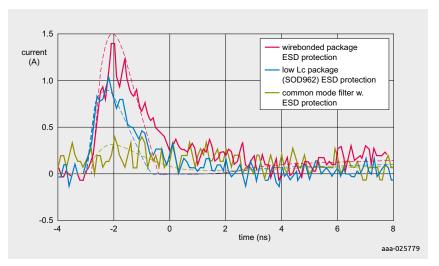

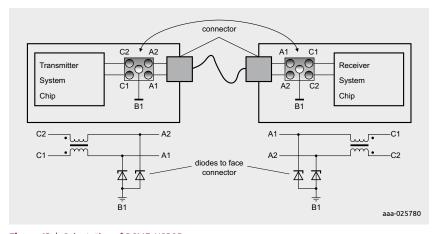

ESD protection components with comparatively long bond wires show a bigger parasitic inductance than components with CSP-like concepts. The DSN0603-2 (SOD962) package has an extremely low parasitic inductance of about 1 nH only. The DFN2510A-10 (SOT1176) package, which is used extensively in computing applications, has an inductance of about 3 nH. With longer traces on the board—I.e. from the connector to the SoC—the inductance of the connection to the IC can be increased. This increase shifts the balance towards a safer region.

Figure 33 | Equivalent Circuit for an IC input pin with ESD protection

# 4.8 Layout and placement hints for an effective ESD protection

As a general rule, it is recommended to put the ESD protection devices close to the entry point of ESD and surge events. Normally this is a connector on a board for user interfaces or board to board connections. The current path through the ESD protection needs to be as short as possible to keep parasitic inductance and resistance as low as possible. As depicted in Figure 33 the board has to be designed in a way that most of the surge current takes the path through the ESD protection and not into the system chip. A comparably higher inductance and resistance in the path towards the SoC helps to reduce the surge energy and voltage at the chip to be protected.

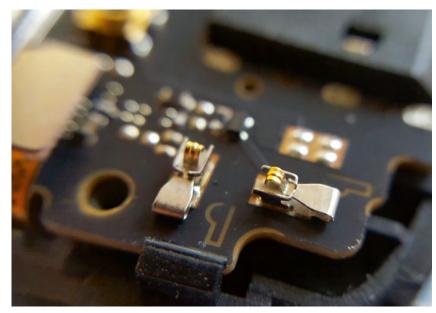

Figure 34 shows a USB Type A connector protected by single ESD protection diodes in the package SOD962. Three lanes are protected, RX+/RX-, TX+/TX- and D+/D-. One pin of each diode is connected without stubs to the data line. The other pin is directly connected to ground with shortest possible wires.

Figure 34 | Layout example with ESD protection diodes in DSN0603-2 (SOD962)

Figure 35 is an example of an ESD protection designed with the multi-line package DFN2510A-10 (SOT1176). For a multiline package, there is less flexibility for the routing compared to single ESD diodes. All signal lines have to go from the connector to the protection device and from there to the system chip.

Figure 35 | Layout example with ESD protection diodes in DFN2510A-10 (SOT1176).

# Chapter 5

SEED (System efficient ESD design) SEED (System efficient ESD design)

A fundamental problem in ESD design is the need for simulation methods that can predict system level robustness. A general misconception is that system level robustness depends on the robustness of individual components. Rather, it depends on several factors. Namely, the robustness of the weakest system-relevant device (usually the SoC that is to be protected), the protection device's properties, other elements in the signal path, and parasitics arising from the board and mounting wires. The idea of 'system efficient ESD design' is to take all these parameters into account in the form of an equivalent circuit or circuit-like simulation to predict system level robustness [8,9].

The quality of the simulation results depends on two factors: The completeness of the system model and the quality of the individual device model, in particular the model of the protection device. The first part can usually be delivered by an experienced engineer. Board parasitics and other, often not desired, model parameters can be extracted from measurements, rule of thumb calculations, or full-wave simulations.

The challenging part is to obtain a suitable model for the protection device. Some devices can be modeled with a modified diode model. Other devices, with snapback and hysteresis, can only be approximated with simple diode models. To fully represent such a device, more sophisticated models must be used which are currently subject to investigations and often exceed the capabilities of ordinary SPICE-based circuit simulators.

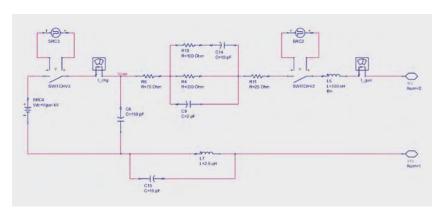

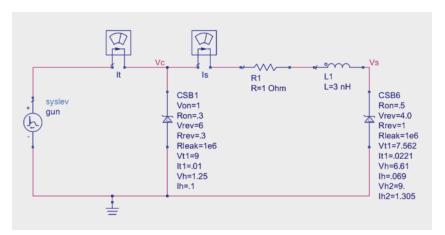

## 5.1 Creation of a system model

The term SEED refers to the concept of connecting an equivalent circuit representation of the system, including the SoC, with a model of the protection device to evaluate protection performance. There are different ways to realize the system simulation. Besides SPICE-based simulations, combinations with other simulation tools like Verilog-A and customized models based on network parameter blocks can be used. Here, the focus is on SPICE based simulations. This approach is very powerful but reaches a limit when the device models cannot be represented as an equivalent circuit in a straightforward way. Some simulation tools like ADS1 offer to import models from other simulation environments like Verilog-A into a SPICE-like simulation workbench. In this sense, the system level simulation can be seen as a SPICE-like circuit simulation, but the internal modeling is no actual SPICE [35].

Independent of the simulation tool used, the frequency rage needs to be determined. Usually a maximum frequency or a minimum time step needs to be set in the simulator. Both have the same meaning and are linked with:

$$r_{min} = \frac{1}{2\pi f_{max}}$$

The maximum frequency to be considered depends on the excitation and effects that are simulated. For high-speed data lines the maximum frequency might be determined by the signal frequency. As a rule of thumb for arbitrary pulse excitation signals, two to five times the bandwidth is taken as the maximum frequency. The bandwidth is usually [10] linked to the rise time with:

$$BW = \frac{0.35}{t_r}$$

Table 5 lists some common excitation pulses with corresponding maximum frequencies. These values are minimum requirements. Highly non-linear effects like snap-backs can increase the maximum frequency even more. It is good practice to use these values as a starting point and increase the frequency to see if the values stay the same, or if higher frequencies need to be considered. Many simulation tools automatically select the frequency or time step. Nevertheless, this is one of the first parameters to check when the results are not as expected.

Table 5: Product overview of automotive ESD protection devices

| Excitation pulse | Rise time (ns) | Max. Frequency (GHz) | Min. Time step (ns) |

|------------------|----------------|----------------------|---------------------|

| IEC 61000-4-2    | 0.7            | 2                    | 0.08                |

| JESD22-A-J114D   | 10             | 0.1                  | 1.6                 |

| IEC 61000-4-5    | 8000           | 0.0002               | 800                 |

| TLP              | 1              | 1.5                  | 0.1                 |

| VF-TLP           | 0.3            | 4                    | 0.04                |

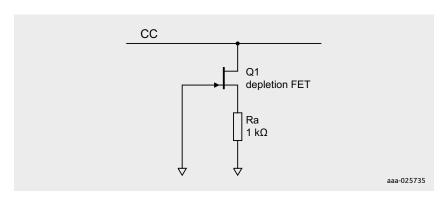

#### 5.1.1 PCB model

There are three practical ways to derive a model for the PCB. If the actual PCB is available in hardware, measurements can be done. If the geometry and material parameters are known, one could do full-wave simulations or use empirical or analytical models. Alternatively, to get a first impression or if the exact routing is not known, one can use rule-of-thumb formulas.

<sup>1</sup> Keysight's ® Advanced Design System

SEED (System efficient ESD design)

If measurements are not possible or impractical, one can use models to derive the S-parameters. There are many full-wave or 2.5D solvers available that can be used to obtain the S-parameters from known geometry and material parameters. Alternatively, there are empirical and analytical models that are available. Giving an overview and introduction of existing methods would go beyond the scope of this handbook, so the reader is referred to [7].

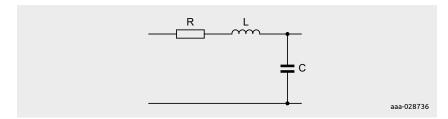

Sometimes, it is not necessary or not possible to have a very accurate model of the PCB. Especially when the design is not fixed, it is reasonable to make some educated guess and proceed with rule of thumb formulas. A good first guess is to use a simple RLC representation of a short transmission line, see Figure 36, and estimate the values from rule of thumb calculations as [12,13]:

$$C = l \xrightarrow{\sqrt{\epsilon_{\Gamma}}} \xrightarrow{FR4} \frac{l}{Z_0} \cdot 7 \xrightarrow{\Omega pF} \xrightarrow{50 \Omega} l \cdot 0.14 \xrightarrow{pF} mm$$

$$L = l \xrightarrow{\sqrt{\epsilon_r} Z_0} \xrightarrow{FR4} Z_0 l \cdot 7 \xrightarrow{\Omega pH} \xrightarrow{50 \Omega} l \cdot 0.3 \xrightarrow{pH}$$

Figure 36 | Equivalent circuit for a short transmission-line

#### 5.1.2 Verilog-A

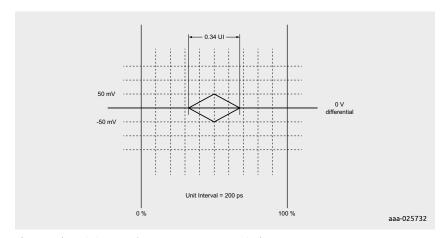

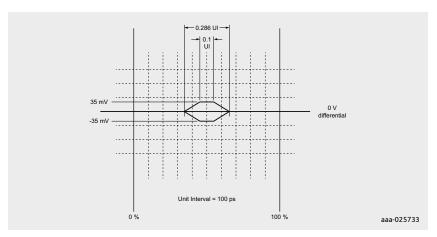

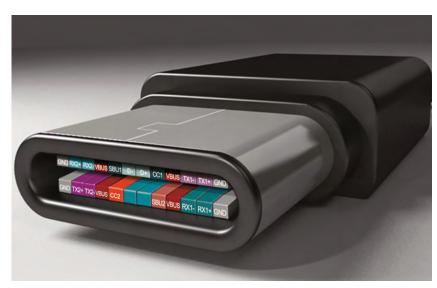

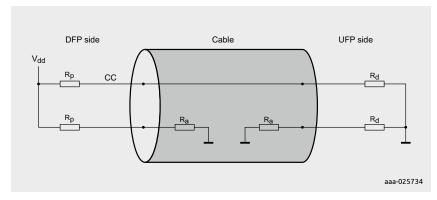

Verilog-AMS (for Analog Mixed Signal) offers the same facilities as VHDL using a different syntax, but licenses for Verilog-AMS are typically only available in larger electronic or semiconductor companies. Verilog-A (for Analog) uses a reduced instruction set from Verilog-AMS and has the advantage of being available to a broader audience. Verilog-A offers a flexible and simple way to implement diodes and snap-back devices, with and without hysteresis w.r.t. the increase or decrease of the current through the device.